New Features in SynaptiCAD Tool Suite v17.0

Waveform Comparison

Waveform Comparison is an optional feature that can be

added to WaveFormer Pro, VeriLogger Extreme, BugHunter, and

TestBencher Pro.

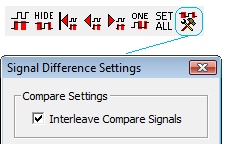

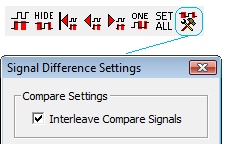

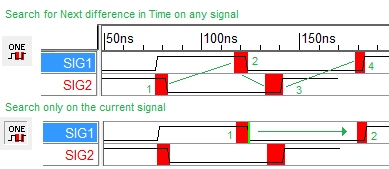

- The new Signal Difference Settings button

quickly lets you setup the properties for doing compares like

whether or not signals will be interleaved on loads or if they

will be displays as a group below.

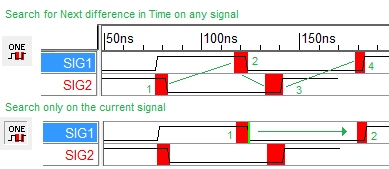

- The new One button gives the ability to

navigate over differences in a single signal. Normally searches

find the next difference in time on any signal. If the One button

is depressed, then the searches will only be done on the current

signal.

- The new Hide button will hide any signal

pairs that do not have any waveform differences. Once signals are

hidden, the View > Show and Hide Signals menu can be used to

re-show the hidden signals.

- Option to perform case-insensitive waveform comparison.

- Faster waveform comparisons, especially when comparing many signals.

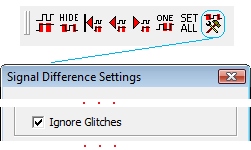

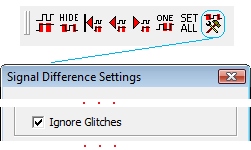

- New option to ignore waveform edge glitches

during waveform comparison. This will filter out zero time

differences between signals.

WaveViewer and GigaWaveViewer (features in all timing diagram editors)

- Waveform compression has been improved, in some

cases as much as 5x over previous versions, which translates into

reduced memory requirements to load large waveform files.

- Compressed files load and save anywhere from 3 to 15 times faster than previously.

- Waveform rendering time was improved, allowing even

truly huge files (e.g. files with over 1,000,000 signals with

gigabytes of waveform data) to be rapidly scrolled.

- 32-bit Windows version can now access up to 3GB of operating system memory (previously the Windows version was limited to 2GB).

- Faster scrolling and reduced memory usage for files with many signals.

- Edge placement dialog is now modeless.

- Faster program startup/shutdown

- Speed up creation/deletion of large numbers of signals.

- Import signals dialog is resizable.

- Support signals up to 66K bits wide.

- Option to display/accept escaped signal names using Verilog escaping syntax.

Timing Diagrammer Pro

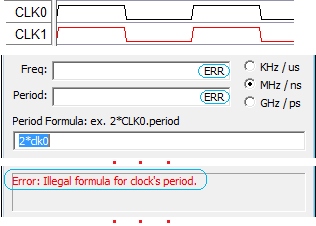

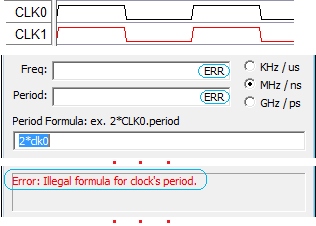

- Improved display of formula information in clock

dialog to simplify spotting errors in clock formulas.

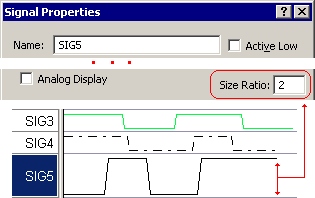

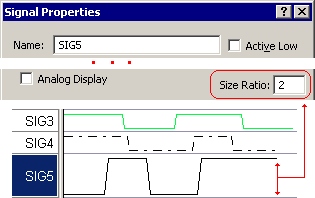

- Height of spacer signals can be changed using the

Size Ratio control in the Signals Properties dialog.

- Better detection of what operations cause a

diagram file to become dirty (previously code was overly

pessimistic and marked diagrams as dirty when no change had

occurred in file).

- Support for "proportional thumb" scroller controls in most windows.

- Support for more modern open/save file dialogs.

- New Monochrome printing feature allows

colored timing diagram objects like parameters, texts, markers to

print as black.

WaveFormer Pro and WaveFormer Lite (includes all features above)

- Signal Properties dialog is faster when

editing properties of many selected signals simultaneously.

- Faster repainting for complex timing diagrams.

- Faster searching through signal names in the signal name window.

- Display message in title bar when a source file

opened for editing is marked "Read Only" by the operating system.

BugHunter (includes all features above)

- New Stepping buttons offer all forms of single stepping and tracing. See Section 2.2 Build and Simulate in the BugHunter manual.

- Step Into - steps to the next line of code and will also step into function calls.

- Step Over Calls - steps to the next line of

code. It does not step into function calls.

- Step Out - executes to the end of the current

function and stops as the function finishes.

- Step With Trace Calls - if the Log button is

depressed then using any of the stepping buttons sends a trace

statement to the simulation.log file.

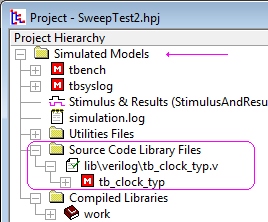

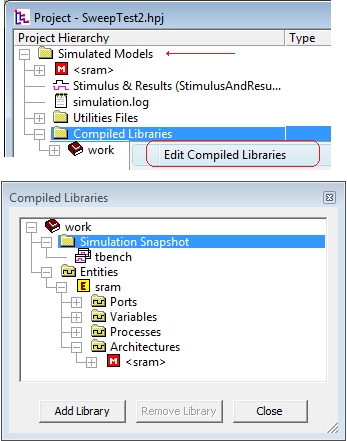

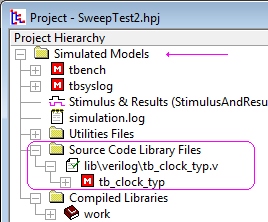

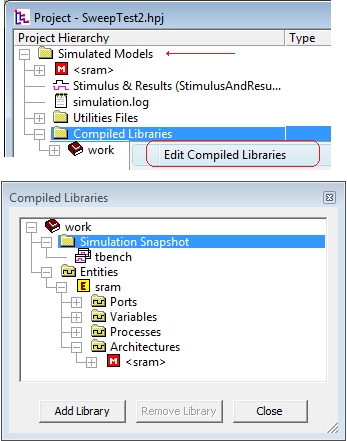

- New Library Search Files folder in the Project

window. See Section 2.9 Source Code Libraries in the BugHunter

manual.

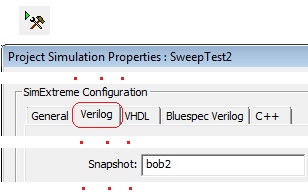

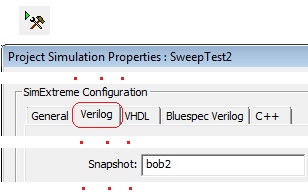

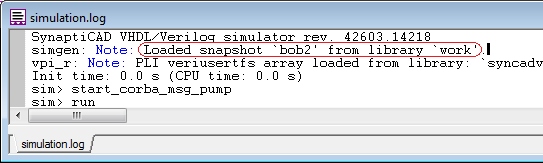

- Snapshots are named builds that allow multiple

runtimes. Pressing the yellow Build button creates a snapshot and

stores it in the current destination library. Pressing one of the

green Run buttons runs the specified snapshot.

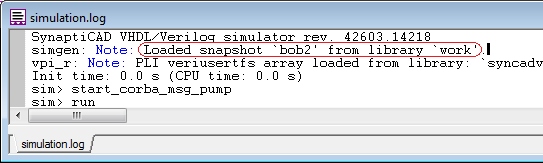

- The simulation log file shows which snapshot is running.

- Display contents of compiled libraries including

generics, packages, processes, procedures, tasks, and function

information in project tree. For more information see the

BugHunter Manual Chapter 2 section on Compiled Libraries (Symbolic

Libraries).

- Support for compiling/debugging SystemC-based projects.See BugHunter Manual Chapter 10 for more details.

- Display resolved net type and delays in the project tree's type field tooltip for Verilog signals.

- Display the full binding (entity+architecture) for VHDL component instances in the type field of the project tree.

- Keyboard commands for collapsing/expanding project tree nodes using and . See BugHunter Manual Chapter 4 in the section on Searching in the Project Window .

- Options in the General tab of the Project Simulation Properties dialog to:

- filter display of parameters and constants in the project tree. Parameters are constants that can affect the compiled "structure" of the design.

- filter display of "empty" processes (unnamed processes that don't declare any variables).

- watch array elements when watching a component.

- watch parameters and constants when watching a component.

- The values of parameters and constants are now visible as soon as a project is built (previously these values could only be viewed when a simulation was running).

- Support watching and setting time variables in VHDL and Verilog simulations.

- Support watching Verilog "event trigger" objects.

- Drag and drop of project files (hpj files) to open them in BugHunter.

- Find subprogram definitions including in the project tree from calls in source code files by right-clicking and selecting the Find In Project menu option.

- Tooltip info displayed for subprograms in source edit windows.

- Improved processing of simulator command-line option fields in the Project Simulation Properties dialog:

- BugHunter can translate simulator options from

any supported simulator to equivalent options required by the

current 3rd party simulator being controlled by BugHunter (our

command-line simulator, simx, does this automatically without

requiring translation by BugHunter). This allows for even

easier switching between different 3rd party simulators.

- Enable the graphical debugger to properly

process source files passed via a command file (i.e. -f file)

in the Compiler options string in the Project Simulation

Properties dialog. This is useful to quickly setup a BugHunter

project that can compile an existing design that is normally

compiled with command-line simulation tools.

- Allow "environment variable substitution"

inside fields of the Project Simulation Properties dialog. See

BugHunter Manual Chapter 2 in the Compiling Command-Line Based

Designs with BugHunter for more details.

- Pre-parser messages are now displayed in the simulation log window and the error tab.

- Option to skip re-parsing of source files when

using Simx as your compiler since BugHunter will have already

compiled the source files during it's preparse operation. This

option is on by default as it speeds up the build process under

BugHunter, but it can be disabled if necessary in the

Simulator/Compiler Options dialog.

- Improved support compiling VHDL designs contained in multiple VHDL libraries (i.e. VHDL libraries such as std, ieee, work, etc).

- Improved support for condition breakpoints across multiple simulators. Support also added for breakpoints inside subroutines contained in a VHDL package.

- New context menu option to show all drivers for a signal from the signal name window.

- Drivers are now shown for concatenated targets in Show Driver windows. We also set the debugger's interactive scope when navigating to a driver in source code from a Show Drivers window.

- Support mixed-language simulations when using ncsim and modelsim as the target simulator.

- Faster communication between the simulator and graphical debugger when adding thousands of watch signals.

- Faster waveform streaming to speed up simulations when watching many signals.

TestBencher (includes all features listed above also)

- "Diagram generated" variables such as state variables are now displayed in Class/Variable dialog.

- Support drag-and-drop reordering of variables in the Class/Variable dialog.

- Folders for Initialized Variables, Input and Output TestVector files.

- Display an informative error message in waveperl.log when parsing an improperly formatted TestVector file.

- Allow adding multiple timing diagrams to Transaction folder.

- Print clock domains for each transactor in waveperl.log during testbench generation.

- Use to_hstring instead of hwrite to handle hex display of std_logic_vectors that aren't multiples of four.

- Display edge time in message when warning about an invalid state on a signal during testbench generation.

- Support for controlling Ncsim(Cadence's Incisive simulator) on Linux.

- Better logging of the distinction between a master and a slave transaction completion.

- Account for radix of signal when initializing variable from testvector file.

- If a testvector file has spaces on the signal label line, split it using spaces and tabs instead of just spaces.

Simx

- Support separate compilation, snapshots, and

compiled libraries for Verilog to reduce time to recompile large

designs. New -L <search_library_name>command-line option added as

part of this change to search through compiled libraries during

elaboration for compiled module definitions. Other new options

associated with these changes include +compile,

+name+<snapshot_name>, and --work &thdestination_library_name>.

- Simx can now be run in "elaboration-only" mode if no source code files are passed on the command-line.

- New simxlib command-line tool for

viewing/manipulating contents of compiled libraries.

- New simx command-line options to accept

command-line options as formatted for 3rd party Verilog

simulators. These options allow easy use of existing regression

build scripts originally created for 3rd party simulators. Use

--mti_options to enable parsing ModelSim-style options, and use

--simx_options to revert to the standard Simx-style options.

- Other new command-line options for simx:

--scd_analysis_details, --scd_recompile,

--scd_psprintf_max_size

- Several optimizations to speed up gate-level

simulation. To disable gate-level optimizations, use

--scd_disable_gateopt. To see information about what gates were

collapsed by this optimization, use: --scd_dump_gateopt_info.

- Faster elaboration of large designs.

- Reduced memory usage during Verilog parsing/elaboration.

- Support for $psprintf, $sformat, and $countdrivers system tasks.

- Simx's preprocessor allows macro definitions inside preprocessor directives for increased compatibility with Verilog code written for 3rd party simulators.

- Support Verilog 2005 syntax for task declarations. This enables tasks without arguments to be called without empty parenthesis (e.g. my_task as well as by my_task()).

- Support for `begin_keywords/`end_keywords compiler directives (Verilog 2005 feature).

- Support SystemVerilog token-constructing operators.

- New PLI/VPI features:

- Added support for check_tf PLI callbacks.

- Added support for setting user-defined system function values using tf_putp/tf_putlongp/tf_putrealp routines.

- Enable the use of a PLI application compiled for ModelSim simulator without needing to recompile the PLI application. Contact SynaptiCAD if you need to do this.

Verilog2Vhdl

- Support for Verilog-2005 multidimensional array translation.

- Added support for translating Verilog-2005 signed rets and nets into VHDL numeric_std.signed data types.

- Allow continuous assignments with undeclared targets to generate correct variable declarations for the targets.

- Support Verilog-2005 event control expressions such as @(posedge foo, posedge bar) as a synonym for @(posedge foo or posedge bar).

- Support for Verilog-2005 localparam keyword.

- Support Verilog-2005 module parameter port lists.

- Support Verilog-2005 named parameter assignments.

Vhdl2Verilog

- Adds range to parameters generated from constants in vhdl2verilog when possible.

- Added -Convert_Integers_for_Synth option which translates vhdl integer literals into fixed-length bit strings.

New Features pages for previous versions:

List of Features in Version 16.0

List of Features in Version 15.0

List of Features in Version 14.0

List of Features in Version 13.0

List of Features in Version 12.0

|