|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

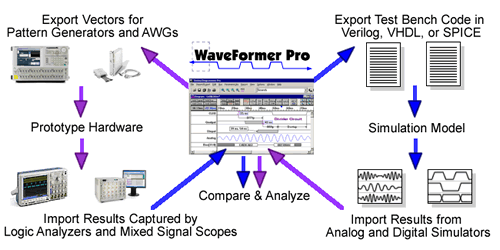

SynaptiCAD connects Tektronix Test Equipment to VHDL, Verilog, & SPICE SimulatorsSynaptiCAD's WaveFormer Pro, works with Tektronix Logic Analyzers, Mixed Signal Oscilloscopes, Pattern Generators, AWGs, and Data Generators and with all Verilog, VHDL, and SPICE simulators. WaveFormer Pro reduces verification time for both hardware prototypes and simulation models by allowing waveform data to be seamlessly moved between the hardware and simulation environments. It reduces test vector creation time, ensures test coverage, and provides an environment for analyzing results and detecting timing problems.

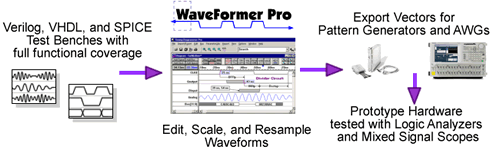

The Tektronix support features are also included in VeriLogger Extreme, our Verilog simulator, and TestBencher Pro, our highest end test bench generator. All three tools have a waveform display and timing diagram editor that can export data to simulator, pattern generator, and data generator formats. They can also import data from logic analyzers, mixed signal oscilloscopes, and simulators. Over 43 file formats are supported and users can add import/export scripts to support other formats. WaveFormer Pro reduces verification time by taking advantage of the parallels between the hardware test environment and the simulation environment. In each environment, the prototype hardware or simulation model has to be stimulated and the results must be analyzed. When one environment is fully verified, WaveFormer Pro can use that data to both stimulate and to analyze the behavior of the design in the other environment. Below are some techniques for using WaveFormer Pro with your Tektronix equipment and simulation environment, and a list of detailed instructions for verifying a design with these techniques. Generate Stimulus for Pattern GeneratorsProgramming a pattern generator with enough stimulus to adequately exercise a hardware prototype has traditionally been a very labor intensive and error prone process. SynaptiCAD's WaveFormer Pro eliminates this problem by allowing the reuse of waveforms from the simulation phase to serve as the waveform stimulus. In addition to direct translation, WaveFormer can generate stimulus waveforms using a combination of graphically drawn signals, timing parameters that constrain waveform edges, clock signals, and temporal and Boolean equations for describing complex, quasi-repetitive signal behavior. Advanced operations on signals such as time scaling and shifting, and block copy and pasting of signal behavior over an interval of time are also supported. This simple, but powerful environment dramatically eases the labor associate with the generation of complex stimulus. The resulting hardware test benches also have the same functional coverage of the simulation models ensuring that the hardware prototype is adequately tested.

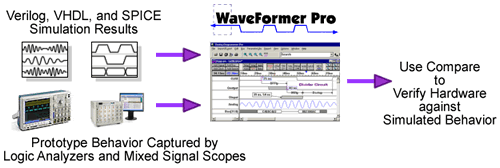

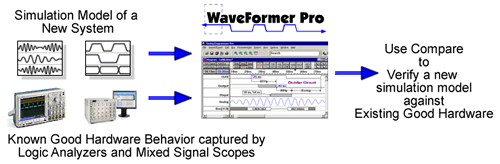

Verify Hardware Response with Simulation ResultsTraditionally, waveform data from a logic analyzer has required visual inspection by an engineer familiar with the operation of the circuit to verify proper operation or to troubleshoot an error. As the number of waveforms and the amount of data captured increases manual inspection is no longer feasible due to the sheer amount of data that must be analyzed. SynaptiCAD's WaveFormer Pro software overcomes this problem by providing a set of automated comparison functions with the ability to compare logic analyzer data to simulation results. Automated comparison guarantees a rigorous check of each data point, ensuring the detection of "small impact" errors that are easily missed during visual inspection of the waveforms.

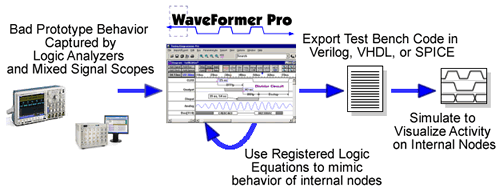

Another important advantage of automated verification is it reduces the amount of knowledge required by the verification engineer to test the system. Rarely does even the designer of a system keep a detailed vision of the operation of all the signals in his design (that's the reason for simulators), yet that is exactly the capability needed to spot a hardware error. The simulation environment, however, knows exactly how the signals should be acting, so it is the ideal tool for identifying any differences between the actual response and the correct response. Simulate and Visualize Activity on Internal NodesOne of the most frustrating problems encountered when debugging a circuit is the inability to see what is happening on all the internal signal nodes of an FPGA or ASIC. A logic analyzer can only show the activity on signals that are brought out on device pins. Unfortunately, many designs are I/O limited. Even when there are no limitations, there are almost never enough pins available to bring out all the useful nodes. To combat this problem, WaveFormer Pro contains a built-in interactive simulation engine that can simulate registered logic equations like those used in FPGAs or CPLDs. Engineers can quickly generate internal signals to check specific points. If a broader view is needed, then WaveFormer can generate a VHDL, Verilog, SPICE or gate-level stimulus file which can be simulated with the original design models to view the entire circuit operation.

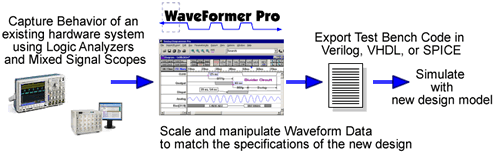

Another benefit of combining a simulation environment with a hardware prototyping setup is the ability to generate complex timing analysis reports. For example, the simulation environment can generate a report of ALL setup and hold timing violations specified between any two signals in a timing diagram regardless of whether this signal is a captured waveform or a simulated waveform (logic analyzers typically only flag the first violation). Setup and hold time violations in ASICs and PLDs are particularly troublesome because the timing violations usually occur on flip-flop inputs that are not directly available at device pins, but are instead a logical function of the device's inputs. Using conventional debugging techniques, these timing violations are extremely difficult to catch because they cannot be directly measured. Using a simulator, we can determine the response of the internal signals, simplifying the detection of timing violations between signals buried inside the chip. Generating Stimulus for Simulation EnvironmentA logic analyzer can capture the raw waveforms from an existing hardware system and convert that data into a VHDL or Verilog test bench. This method is particularly effective for testing FPGA's and ASIC's which interface to existing systems. Instead of spending weeks developing a test bench the engineer can capture real world stimulus and begin simulating within minutes of capturing the data. WaveFormer's built-in timing diagram editor can also scale and manipulate the captured waveforms. For example, assume a set of waveform data was captured from a current generation system running at 50Mhz and the new (not yet completed) system will run at 90Mhz. The captured waveforms can be scaled to the higher speed and then used to test the new system's simulation models.

Interface Functional TestingOften the system being designed is the next generation of an existing product with similar functionality. In this case, the new system must generally mimic at least part of the interface of the older system. By performing a waveform comparison between the old system and the new design, correct functioning of the new system can be assured.

Detailed Instructions |

|

|