|

New Features in SynaptiCAD Tool Suite v15.0

Waveform Viewers and Timing Diagram Editors

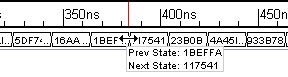

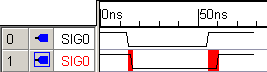

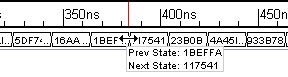

- The mouse tooltip now displays the next and

previous states of bus segments when the mouse hovers over a state

transition. This feature can be disabled by unchecking the View >

Show State at Cursor menu. See Section 1.5 Measuring Time and State

values for more techniques on viewing states.

- Bus segments automatically show partial extended

state data when the segment is too small to fit the entire state

within the segment. Two trailing dots indicate the value is only

partially shown.

- Markers labels "float" at the top of timing

diagram windows so that as you scroll vertically through the

diagram you can still see the marker display label (Section 6.5

Marker Lines).

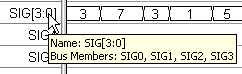

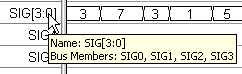

- Hover over a Group Bus name to display member

signals of the bus in a tooltip (Section 3.2 Group Buses).

- The timing diagram editor can support Japanese and

other non-English fonts.

- User-defined radices can now be saved in filter

files, so you can store your own customized radix for viewing the

imported waveform data from a VCD or other waveform source file

(see Section 11.2 Import General Instructions ).

Timing Diagram Editor Improvements (all timing diagram products)

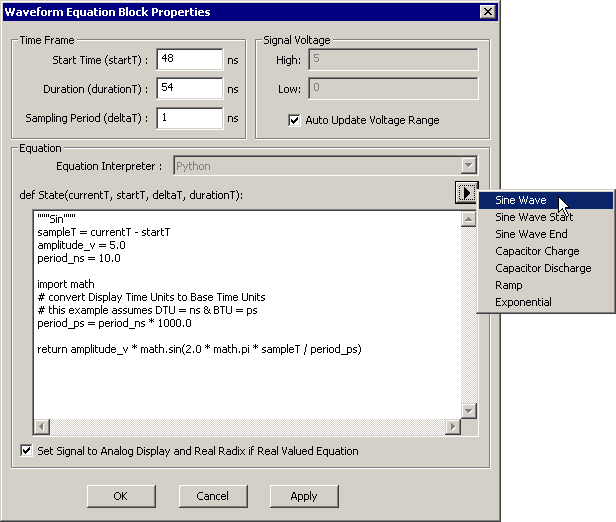

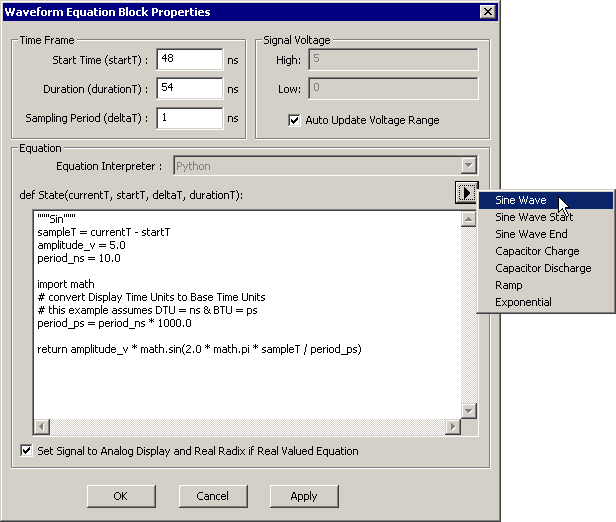

- New Python-based Waveform Block Equations can be

edited after a waveform is created, unlike the older State and

Waveform equations. These are especially useful for analog

waveforms which can be difficult to get right on the first try. See

Section 8.2 Waveform Equation Blocks for editable Analog waveforms

for information on how to create waveform equation blocks.

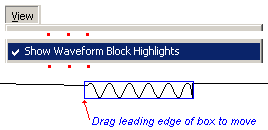

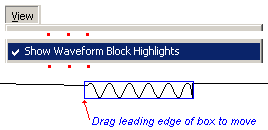

- There is a special view mode that highlights all

the Waveform Block Equations in a diagram with blue rectangles so

that you can easily identify and edit the waveform equation blocks.

Double clicking on a waveform block in this mode will automatically

open a dialog to edit the equation block. A block can be moved by

clicking and dragging the edge just preceding the block.

- The Auto Save for Recovery feature temporarily

saves timing diagrams at specified intervals so that data can be

recovered in the event of a premature termination of the program

(e.g. in case of a power failure).

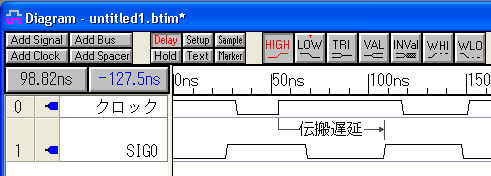

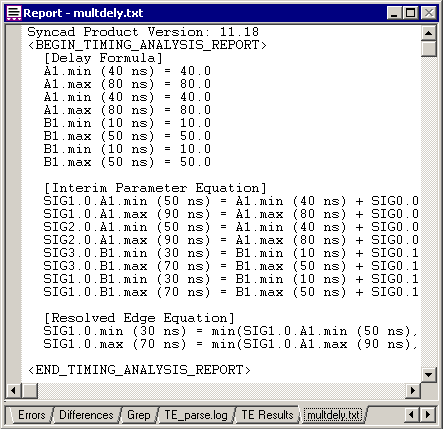

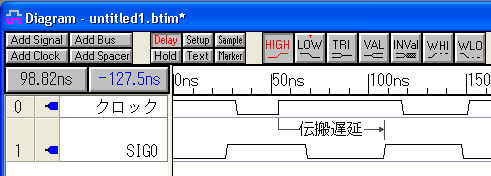

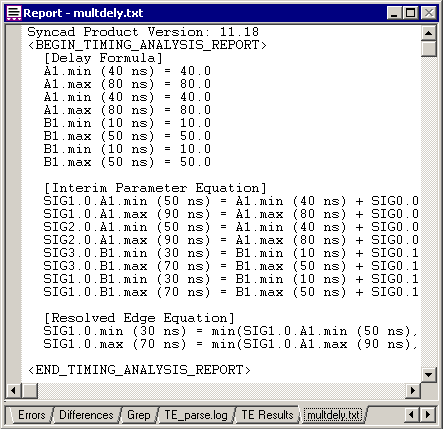

- Delay correlation information has been added to

the Timing Analysis Report. This report is generated when a diagram

is saved with a file type of Timing Analysis Report. The report is

saved to a file and also displayed in the Report window.

- WaveFormer Pro can read files generated by the

MSO4000, MSO3000, and MSO2000 series mixed-signal oscilloscopes

from Tektronix (see Section 11.14 Tektronix Logic Analyzer &

Oscilloscope - Import ).

- It is now ten times faster to drag-and-drop all

of the transitions on one signal by holding down the "1" and "2"

number keys while dragging. Holding down just the "1" key moves all

the edges to the left, and the "2" key moves all the right.

- Users can now manually edit TIM files in a text editor.

- New icons with little boxes around them indicate

that a signal is a "compare" signal.

- Integration with TI's SystemC-based High End Timer

simulator. This can be downloaded directly from the TI web site at

http://focus.ti.com/docs/toolsw/folders/print/het_ide.html .

- Improved HTML-based help for UNIX.

VeriLogger Extreme

- Added support for 64-bit simulation under 64-bit

Windows operating systems. To compile 64-bit simulations you also

need to install the free Windows SDK 7 from Microsoft. In the

BugHunter & VeriLogger Manual see Section 5.1 VeriLogger Extreme

tools: Simx and Simxloader for downloading details.

- Support for Xilinx SecureIP models.

- Cycle-based and non-blocking assignment

optimizations result in faster simulation times (e.g. 8x faster on

OpenCores ac97 benchmark).

- Faster simulation of timing checks.

- Reduced memory usage by over 4x for large designs.

- Improved code generation results in smaller

simulator executables and faster simulation build times.

- Faster dependency checking during simulation rebuilds.

- Enhanced PLI 1.0 and 2.0 support (all VPI and ACC

functions now supported except put_delays/attribute functions).

- Support -g/-G/+defparam options to override

parameter values from the command line. In the BugHunter &

VeriLogger Manual see Section 5.7 Simx Override Parameter Values

Options.

- Internally tested against Actel and Altera IP Cores.

BugHunter HDL Debugger Features

- NEW Schematic Display using BugHunter Pro and GOF.

In the BugHunter & VeriLogger Manual see Chapter 10: Schematic

Viewing of Gate Level Designs.

- Open Gates-on-the-Fly schematic windows from

components in BugHunter's hierarchy window to analyze gate-level

designs.

- Double click in the new scope column of a Show

Driver window navigates to the scope instance. In the BugHunter &

VeriLogger Manual see Section 2.5 Find Drivers.

- Change driver signal values from a Show Driver window.

- Watched signals add after the last selected signal

(same behavior as when pressing "Add Signal" button). In the

BugHunter & VeriLogger Manual see Section 2.2 Watching Signal and

Component Waveforms.

V2V = Verilog2VHDL and VHDL2Verilog model translation

- New -v95 and -v2001 options to specify style of

Verilog code to translate to.

- The No_Component_Check is now turned on by default

when translators are executed from the BugHunter GUI. This allows

translations to proceed when not all module or entity definitions

have been parsed by the translator. This is useful when translating

files individually inside the BugHunter GUI. In the BugHunter &

VeriLogger Manual see Section 9.2 VHDL2Verilog Translation Options.

- VHDL2Verilog supports constants defined using record types.

- Many bug fixes.

Gates-On-The-Fly Netlist Editor

- GOF now supports 64-bit Linux operating systems.

- New read_file api can import static timing analyzer data.

- New fix_setup and fix_hold API calls for

automatically fixing setup and hold violations detected by static

timing analyzers.

OEM - 3rd Party API enhancements

- Added API functions for controlling signal and

marker color, setting marker type, and get and set of tooltip

display.

- New syncadlauncher dll allows a third party

application to launch the syncad GUI and perform basic control of

syncad.exe without including a CORBA ORB.

New Features pages for previous versions:

List of Features in Version 14.0

List of Features in Version 13.0

List of Features in Version 12.0

|