10.2 Waiting for Signal Transitions or Conditions |

|

|

|

10.2 Waiting for Signal Transitions or Conditions |

|

|

In TestBencher and Reactive Test Bench Generation, either samples, markers, or sensitive edges can be use to make a transaction wait for an event or series of events before continuing to execute. Below is a chart of the different methods of waiting and the recommended usage for each method.

Wait On |

How Long |

Construct |

Help/Settings |

One event |

Block indefinitely or until diagram times out |

Sensitive Edge |

|

One or more conditions (e.g., signal states) |

Block indefinitely until all conditions are true |

Wait Until Marker |

|

Samples |

Section 3.3: Samples that Block Clock Domains to make a sample block, check Blocking and uncheck Full Expect (so it triggers when the condition is true) in the HDL Code Generation dialog. |

||

One event or condition |

Block until time out |

Sample with window |

min != max multiplier == 1 |

One event or condition |

Block until time out |

Sample with Multiplier |

Section 3.2: Sample Checking and Actions min == max multiplier > 1 |

Several events or conditions across several clock cycles |

Each sample may block with time out |

Several samples chained together (first samples will block subsequent samples |

Section 3.4: Samples Triggering a delayed transition or another Sample |

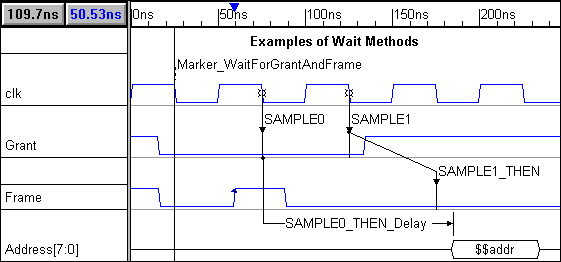

Below is an example of timing diagram that demonstrates these techniques for waiting.

•The Marker called Marker_WaitForGrantAndFrame is a wait until marker type with the condition of (Grant===0 && Frame ===0) {the condition code is in the generated language, in this example Verilog}. This marker will block the transaction until the condition becomes true. •The rising edges on the Frame signal are sensitive, and are drawn with the little blue arrow on the rising edges. This will cause the diagram to wait for the rising edge to occur. •The Sample called Sample0 is setup as blocking and non-full-expect with a multiplier of 3. The Multiplier is the sample's time out. Checking the blocking box causes the sample to block the triggering clocked sequence until it times out or until the condition becomes true. Disabling the Full Expect box means that the sample will not expect the drawn condition to be true during the entire window. Instead it will continue sampling as long as the condition is NOT true and the time out has not been reached. •Sample0 also has a conditional delay, SAMPLE0_THEN_Delay, so that when it passes it will cause the value passed into $$addr to be written out to the Address signal. If Sample0 times out then the Address signal never gets driven. •The samples Sample1 and Sample1_THEN check for Grant and Frame to be true over successive clock cycles. They are defined using the same settings as Sample0 in the previous example except the multiplier is set to 1. |

If a Sample has a multiplier of 1 and no window defined at simulation, then the blocking check box has no effect on the behavior of the Sample. This is because the Sample will execute and then immediately pass or fail depending on the condition (if the sample was windowed, it potentially blocks the clock domain until the sample's timeout time, but without a window, the "timeout" occurs immediately).