3.3 Samples that Block Clock Domains |

|

|

|

3.3 Samples that Block Clock Domains |

|

|

A sample can also be made to block other graphical elements in the diagram by using the Blocking check box in the Code Generation Options dialog. If Blocking is enabled then other elements in the same clocking domain as the sample will be paused until the sample completes. If Blocking is disabled, the other graphical elements will continue to function regardless of whether the sample condition is satisfied. Blocking samples are drawn with a solid arrowhead, and non-blocking samples have a hollow arrowhead.

Set the Blocking Control:

•Double-click on the Sample name to open the Sample Properties dialog. •Press the HDL Code button to open the Code Generation Options dialog. •Check the Blocking box at the bottom of the dialog. |

|

What gets Blocked:

Samples block other graphical objects that are triggered from the same clocking domain. If a blocking sample is triggered off the rising edge of a clock signal, then the sample can block all other elements that are also attached to the same positive edge. The sample will block until the "if condition" triggers. If the clock is a system clock for other signals in the diagram, even the driving waveforms will be blocked until the the sample finishes executing. Elements that are in a different process/clock domain, continue to run in parallel. The source code for a timing diagram will explicitly state each object's clocking domain. To view the source code:

•Save the timing diagram to generate new code. •Then Press the Source Code button to open an editor and view the code. |

|

•In the top of the generated source code file, there is a Clock Domain comment section which lists the triggering processes for the diagram. •In this code, SAMPLE0 can block all of the signals, markers, and delays that are triggered from the positive edge of GClock and that occur after SAMPLE0 triggers. However, SAMPLE0 cannot block DBUS_SetupCheck, because that construct is triggered from the negative edge of the clock. |

|

Code Generation and Clocking domains for Samples:

The code for samples will sometimes be generated in a separate process and sometimes within the clock sequence process that triggers it (in-line). Whenever possible, the sample code will be generated in-line to make it easier to debug the generated code. However, if the sample is non-blocking and needs to wait for simulation time to pass, then that sample will be placed in its own process or task and triggered by the sequence at the appropriate time. Some examples of samples that need to wait for simulation time to pass are windowed samples or samples that are delayed from their triggering point.

The sequence process that triggers a sample is determined from the combination of the triggering edge and the Samples Properties dialog clock and edge type settings.

Triggering Edge |

Clock and Edge Type |

Triggering Sequence |

Time based trigger |

ignored |

Unclocked Sequence |

Attached to an edge |

Unclocked or matches triggering edge |

Triggering edge's sequence |

Attached to an edge |

Different than triggering edge |

Clock sequence from dialog with a level sensitive check on the triggering signal |

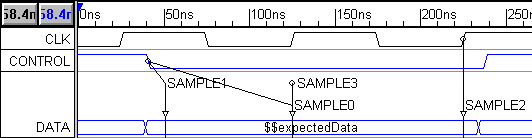

The example diagram below contains three domains: CLK_pos, CONTROL_neg, and Unclocked.

•CLK_pos: This is a clocked diagram so most of the graphical elements were automatically created with the clock/edge already set to CLK and pos edge in the Properties dialog of the element.

•SAMPLE2: triggered from the third positive clock edge.

•SAMPLE0: at second positive clock edge, a level sensitive check is performed on the CONTROL signal and if it is 0 then the sample will trigger. If instead of a level sensitive check on CONTROL, you want to perform an edge sensitive wait on CONTROL, then set the falling edge sensitive check box in Signal Properties dialog for the CONTROL signal.

•CONTROL_neg: When SAMPLE1 was created we used the Sample Properties dialog to change the clock setting to unclocked. This setting change will allow SAMPLE1 to be triggered immediately when the CONTROL signal goes negative (compare this to the behavior of SAMPLE0 above, which triggers synchronously with the clock).

•Unclocked sequence: SAMPLE3 is an absolute sample (not attached to an edge) so it will be placed in the unclocked sequence. SAMPLE3 will trigger at 125 ns after the beginning of the transaction.

More examples and other Blocking Constructs

Section 10.2: Waiting for Signal Transitions or Conditions shows an example using all three blocking features: samples, Wait Until Markers, and Sensitive Edges.