10.3 Burst Mode Transactions |

|

|

|

10.3 Burst Mode Transactions |

|

|

Burst Mode Transactions usually process one or more cycles depending on information received at simulation time. TestBencher can model burst mode transactions using a combination of marker loops, parameter variables, and samples. The basic design for a burst mode transaction is as follows:

1.Draw a timing diagram that represents the smallest possible transaction. 2.Use a marker loop to define the beginning and ending of the repetitive section. 3.If it is a master transaction, use an input variable to pass in the number of cycles to process. This variable will be used in the condition statement of the Marker loop. 4.If it is a slave transaction, you will use one or more samples chained together to determine if the burst transaction should continue. |

The PCI example in the SynaptiCAD>Examples>TestBencher directory has examples of both master and slave burst mode read transactions.

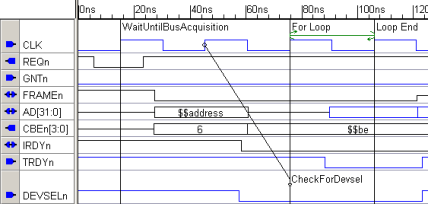

•After opening the PCI example for your language, drill down into the Project Library to find the read cycle of the Master sub-project. •Below is an example of a simple burst mode master read cycle. |

|

•The marker, WaitUntilBusAcquisition, will cause the transaction to wait until the condition (GNTn === 0 && FRAMEn === 1 && IRDYn === 1) is true (Section 5.4: Wait Until Markers). •The sample, CheckForDevsel, checks the DEVSELn signal and if it is active low then the transaction proceeds normally. If it fails, the transaction aborts (Chapter 3: Transaction Samples). •A diagram variable called dataCycles is defined as a transaction input with a type of integer. When the transaction is called, dataCycles will carry the number of cycles that the master read will execute (Section 6.1: Variables). The For Loop uses the dataCycles variable to determine how many read cycles to perform (Section 5.5: Loop Markers). •Two state variables, address and be, are also transaction inputs (2.4 Waveform States with Variables and Conditions). |