10.7 Different ways to bring in External Models |

|

|

|

10.7 Different ways to bring in External Models |

|

|

TestBencher’s TLMs can be used with external models from any of the languages supported by TestBencher, with other TestBencher TLMs, and with TestBencher Reference Models. TestBencher automates the process of hooking up the project TLM to other models that exist in your system by using information contained in the different folders of the project.

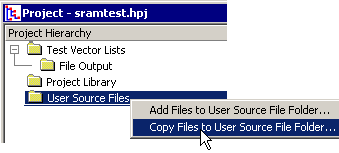

VHDL and Verilog Models

External VHDL or Verilog models are first added to the User Source Files folder and then the Extract MUT Ports function extracts the model information and makes it available to TestBencher. This is discussed in Step 2: Add the MUT to the Project and Step 3: Extract Ports into Template Diagram.

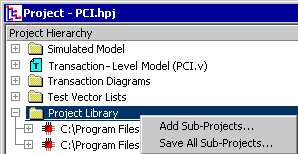

Other TestBencher TLMs

Other TestBencher TLMs are first added to the Project Library folder and then instantiated using the context menu functions. This process is detailed in Section 9.1: Sub-Projects and Section 9.2: Component Instances of Sub-Projects. The TLMs should be of the same generation language as the main TestBencher project.

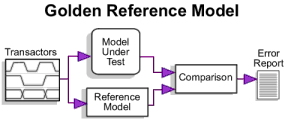

TestBencher Reference Models

TestBencher can generate golden reference models that run in parallel with a VHDL or Verilog RTL model. Golden reference models are high-level behavioral descriptions of a design and are used to compare to the results of an RTL-level model during simulation. When this feature is turned on, TestBencher handles all of the code generation and hook-up of the model. This is covered in Section 9.3: Golden Reference Models.