Step 2: Add the MUT to the Project |

|

|

|

Step 2: Add the MUT to the Project |

|

|

The Model Under Test (MUT) files of the design should be added to the project. TestBencher will use these files to extract the signal and port information for use in the transaction diagrams and will use the file information to enabling compiling your design with your simulator via the Build button.

Copy or Add the MUT's source files to the project:

•Right click on the User Source Files folder and either add or copy your design files to the project. •The Copy menu copies the source file to the project folder and adds the copy to the project list. The Add function adds the file and its path without making a copy. Files can also be added by choosing the Project > Add User Source File(s) menu from the main bar. |

|

•If your MUT requires definitions from a package compiled into a different library, follow the steps in Section 8.5: Parsing Package Files into Libraries to ensure these packages are properly parsed. If your MUT parse does require files to be compiled into multiple libraries, you will probably need to directly set your desired model under test after the first parse, then parse again (see Step 3: Extract Ports into Template). |

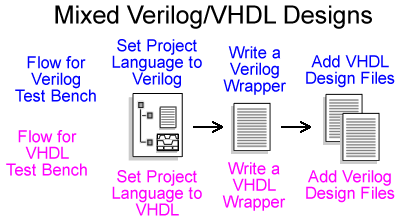

Mixed VHDL and Verilog Designs:

If you have a multiple-language design or if you are more comfortable working in a particular HDL language, then the generated test bench and the design model do not have to be in the same language. You will need to write a wrapper module in the test bench generation language that instantiates the models in the other language. You will also need a multiple-language simulator to compile and debug the design.

•In Step 1, when you create the project, set the language to be the language that the test bench will be generated in. Also set the simulator to the name of your multiple-language simulator. •Create a new file containg a wrapper module in the test bench language that instantiates the design model and maps signal types between the two different languages. The syntax for the instantiation of the design module will specified by your simulator. The ports for the wrapper will be the signals that the testbench drives and observes. •Add the design files to User Source Files folder as described above. TestBencher can parse both VHDL and Verilog files and also send the files to the multiple-language simulator. |