10.8 Different ways to Loop |

|

|

|

10.8 Different ways to Loop |

|

|

There are three different ways to loop.

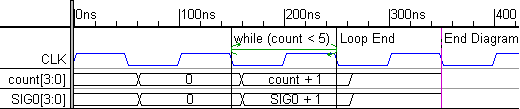

1) Use Markers to loop within a diagram

Markers can be used inside a timing diagram to create a loop around a specific clock domain (like all objects and waveforms triggered off the negative edge of a clock). Section 5.5: Loop Markers has more information on the creating the loops and setting the clock domains.

2) Use code at the Sequencer Lever to repetitively call a transaction

Inside the Sequencer Process of the Transaction-Level Model, you can repetitively call a transactor by writing loop code in the generation language. Below is code excerpt from the Sweeptest2.hpj examples located in the SynaptiCAD\Examples\TestBencher directories. In these examples, each time the loop executes it calls a write then a read transaction using a different delay value to see when the circuit starts to fail. See Section 7.1: Template, Sequencer, and Transaction Calls for more information.

Verilog |

// Sequencer Process for (delay0 = 32.0; delay0 > 15.0; delay0 = delay0 - 5.0) begin Apply_tbwrite( 'h55 , 'hee , $realtobits(delay0) ); Apply_tbread( 'h55 , 'hee , $realtobits(delay0) ); end |

VHDL |

-- Sequencer Process for i in 0 to 5 loop delay0 := real (32 - (i * 5)); Apply_tbwrite( tb_Control, tb_instancePath, x"F0", x"AE", delay0); Apply_tbread( tb_Control, tb_instancePath, x"F0", x"AE", delay0); end loop; |

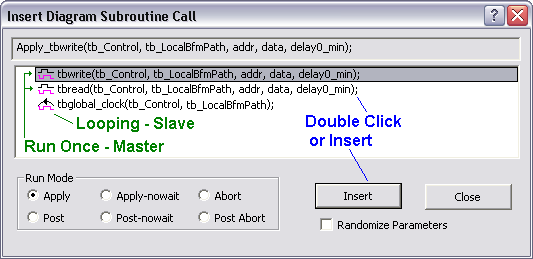

3) Apply the transaction in Looping Mode and make an abort call.

Inside the Sequencer Process of the Transaction-Level Model, you will make calls to apply the transactions. A transaction can be applied in a looping mode that will make it continually run. Section 7.1: Template, Sequencer, and Transaction Calls has more information on the different types of apply calls. Looping transactions need to be aborted after the testing is complete.

Verilog |

// Sequencer Process Apply_tbglobal_clock_looping_nowait; ... Abort_tbglobal_clock; |