6.10 (Verilog) Initialize Array from File |

|

|

|

6.10 (Verilog) Initialize Array from File |

|

|

In Verilog, Project-level array variables can easily be initialized with data from a file during the test bench generation process. For VHDL, see Section 6.11 (VHDL) Initialize Array from File (the way to access the variables differs between the languages). The data is read from the file during test bench generation (not at simulation time) and written in the code of the top level test bench. This technique is very useful for Verilog test benches, because the Verilog code generator does not support reading file input during simulation as VHDL does (i.e. Section 6.9 Input Data Dynamically from a File (VHDL)).

In Verilog, you will first add the data file to the Initialized Variables folder, then press the Make TB button to generate the code. Inside a timing diagram, use @columnname[index] notation to access the file variable, where index is the row number of the data to use.

1) Create a data file:

•The data file should be in the spreadsheet file format with only one column that contains the data for the array. The file format is described in Section 6.7 SynaptiCAD Test Vector File Format. Note that the column name should NOT be the same as a signal name used in the a diagram. The column name will become the variable name and needs to be unique. |

|

2) Create a project-level array variable linked to the data file:

•Under the Test Vector Lists folder, right click on Initialized Variables to open the context menu. Put the data file in this folder using either the Add... menu which adds the file without moving it, or the Copy... menu which copies the file to the Project directory and then adds it. |

|

Investigate what got created when you added the file:

•Right click on the Class Library List folder and choose Classes and Variables to open the Classes and Variables dialog. |

|

•Select the Variables tab, and notice that a variable has been created that is named after the column name of the data in the file. The Structure is of type array, the size indicates the number of rows of data, and the MSB/LSB/Data Type should match the information in the file. |

![]()

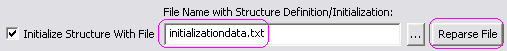

•At the bottom of the dialog, notice that Initialize Structure with File box is set and the file name is listed. |

•If at some point the data file column name or size is changed, you can use the Reparse File button, located at the bottom of the dialog, to update the file variable. |

•Note: After adding the file, you can double click on the file name to view the data or edit it. |

|

3) Generate the Test Bench:

•Press the Generate Test Bench button on the simulation button bar. This collapses then expands the macros in the template file. |

|

Investigate the code that was generated:

•Double-click on the Transaction-Level Model folder in the Project window to open the template file. |

|

•Search for the variable that you attached to the file. The code generation should look something like the image shown. |

|

4) Reference the Variable inside the Diagram

•Double click on a waveform segment to open the Edit Bus State dialog. •Use the > button to find the file variable or type it into the Virtual edit box. Make sure to use the @ symbol to indicate that it is a project level variable. |

|

•Since this is an array, you must add an index to the variable name. For example, the index can be a hard-coded value like "4" in @testdata[4], a variable that can be passed into the diagram each time it is called via the Apply call, or an index variable created by a Marker-generated for-loop. •To make a variable that is an input to the timing diagram transaction, press the View Variables button on the diagram window and create a variable that has a direction of input. Then use this variable as the index to the array variable. |

|