11.1 Signal Names for export and import |

|

|

|

11.1 Signal Names for export and import |

|

|

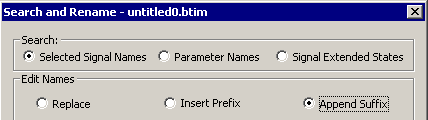

Signal names, parameter names, and bus states can be globally searched and replaced in the diagram based on a regular expression. When a file is imported from a simulator or logic analyzer, the signal names sometimes have extra information, like hierarchical model names, that need to be striped away before exporting to the next format. Also, signal names with periods are treated as if the entire name is surrounded by escape characters. This section shows examples of the regular expressions that can be used in the Search and Rename dialog, but more information about parameter name searching is covered in Section 5.6 Parameter Window, and the signal extended state search is covered in Section 3.1 Edit Virtual Bus.

Search and Rename Signals, Parameters, and Waveform states:

•Select the signals whose names you'd like to change, and choose the Edit > Search and Rename menu to open the Search and Rename dialog. •Choose the type of object to search for: signal names, parameter names, or extended states. |

•To strip off part of a name, select the Replace button, enter the search pattern into the Old Name box, and enter the pattern that you want to search for, and enter the replacement string in the Signal Name Replacement box •In the example, "top." is being replaced by a "blank". The pattern can also match to any part of the string (not just the beginning). |

|

•To insert text before or after the name select either the Insert Prefix or the Append Suffix button. •Then enter the text to add to the names in the edit box. |

|

•Sometimes during a Parameter rename operation the program can encounter a duplication conflict when a parameter is being renamed to the same name as another parameter, but that the two parameters differ in properties (different min and max times) or types (delay, setup, hold). If such a conflict is found the Duplicated Parameter Names dialog will open so that you can fix the conflict. This dialog is described in Section 10.4 Merging Diagrams, because this type of conflict happens frequently during a timing diagram merge. |

Signal names and the hierarchy/scope character (".")

If your signal name contains one or more periods, the timing diagram editor will assume that the signal name is meant to be hierarchically scoped within the source code. For example, a signal named Foo.Bar will be treated as signal Bar in a module named Foo. If you want to avoid this automatic scoping, add backward slashes to the beginning and end of your signal name to 'escape' it. For example, a signal named \Foo.Bar\ will be treated as a signal at the top level of the scope hierarchy.

If your signal name contains two or more directly adjacent periods (foo..bar), the timing diagram editor will automatically 'escape' the signal name, as there are no characters in between that could be a scope name. For example, a signal named Foo..Bar will be treated in the same manner as if its name were /Foo..Bar/.