9.5 Signals and Ports for Components dialog |

|

|

|

9.5 Signals and Ports for Components dialog |

|

|

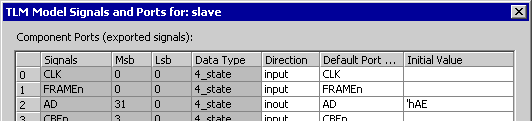

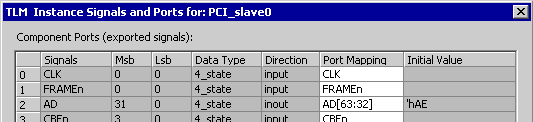

The Signals and Ports dialog is used to view and edit the ports and internal signals of Transaction-Level Models and definitions as well as the port mappings of Component Instances. TestBencher automatically creates certain signal and port information based on the Model Under Test and diagram ports. Internal signals are also created automatically based on the specified port mappings for component instances.

To open the Signals and Ports dialog:

•Right click the item to be edited (a Transaction-Level Model, Component Definition or a Component Instance) and select Signals and Ports from the context menu. This will open the Signals and Ports dialog. |

|

While this dialog is open, you can select any Component or Component Instance in the Project window and edit the signal and port information associated with that object.

Editing signals and ports with the dialog:

•The signals and ports that have gray cells are automatically generated for the MUT and diagram ports, as well as from port mappings that have been defined from child projects. These fields are fixed and cannot be edited by the dialog. •For Component Definitions, internal signals can have their direction edited, and ports can have either the direction, default port mapping, or the initial value edited. |

•Component Instance internal signals cannot be edited, and ports can have only the specific Port Mapping for the instance modified. |

•New component level signals can be added when editing signals and ports for the Transaction-Level Model (the component definition) by clicking the New Signal button. These signals can be made ports by changing the Direction of the signal from internal to input or output, or by dragging and dropping the signal from the bottom grid tree to the top. Note that when editing a Component Instance, the signal and port definitions cannot be changed. •Port Mappings can be specified by double clicking a cell in the Default Port Mapping or Port Mapping column. When working with a Component Definition, the Default Port Mapping specified provides a default that will be used for the instances of the component being edited. If a Component Instance is being edited, then the actual Port Mapping for that instance is being specified. •If the signal that the port should connect to is not yet defined in the owning component, just type the name of the new signal into the Port Mapping column. TestBencher will automatically create a new signal in the owning component for this connection. •A bit slice can be specified for each Port Mapping. TestBencher allows a bit slice to be specified as part of the port mapping, so that the connecting signal may be larger than the port. If the specified bit slice for the port mapping is outside of the connecting signal’s bit range in the owning component, TestBencher will automatically combine the two bit slices in the connecting signal. Each time the test bench is generated the bit ranges of component signals will be verified. This means that if a bit range is extended, but then no longer needed it will be reduced to its original size. The only case in which this will not happen is if the signal was explicitly added in the Signals and Ports dialog by the user. In this case, TestBencher may need to extend the bit range, but will never reduce it. The Component Instance Signals and Ports image above shows an example of a bit slice specification for port AD. •The Initial Value column provided for ports when editing a Component Definition allows an initialization for the port to be provided. The string entered in this field is placed directly into the generated source code without formatting. This value can not be edited at the Component Instance level. The images above show an example of specifying an initial value for port AD. |

The Transaction-Level Model has both exported signals and internal signals. By default, all signals that are generated by TestBencher are internal, but the Component Signals and Ports dialog allows these signals to be exported by simply changing the direction of the signal.