4.3 Creating Continuous Setups and Holds |

|

|

|

4.3 Creating Continuous Setups and Holds |

|

|

Continuous setups and holds can be created for any two signals in a timing diagram. A continuous setup or hold is created in the Advanced Register and Latch Controls in the Signal Properties dialog. Continuous setups and holds can be useful in ensuring that a data signal remains stable long enough to be written at every clock edge, for example. This section will describe how to create a continuous setup or hold that will persist for the duration of a timing transaction's execution.

This feature is currently only supported in VHDL and Verilog, because it uses a feature called simulated signals. The simulated signals can be used to create registered and latch logic, so there are several optional controls that you can choose to use. This feature is not supported in WaveFormer Lite with Reactive Test Bench Generation Option.

To Create a Continuous Setup or Hold:

•Create an extra signal that will hold the equation that performs the continuous setup or hold on the two signals in the design. •Double-click on the extra signal to open the Signal Properties dialog. |

• In the Boolean Eqn box, enter the name of the signal to monitor (pick the non-clock if one of them is a clock). •In the Clock box, select the other signal and choose an Edge/Level to compare the signals on. •(OPTIONAL) The Set, Clear, and Clock Enable are optional signals that model the set, clear, and clock enable lines of the register or latch. These lines can be active low or high and synchronous or asynchronous depending on the settings in the Advanced Register and Latch Controls dialog. |

|

•Press the Advanced Register button to open the Advanced Register and Latch Controls dialog. •Enter a Setup time, a Hold time, or both times. |

|

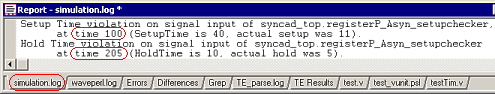

•Setup: Describes the time for which the input must be stable before the clocking event. If a min/max time pair is entered, Setup will use the min time. Any violations of this setup time will be reported to the simulation log file simulation.log, shown in the report window. •Hold: Describes the time for which the input must remain stable after the clocking event. If a min/max time pair is entered, Hold will use the min time. Any violations of this hold time will be reported to the simulation log file simulation.log, shown in the report window. |

Continuous Setup and Hold After Simulation

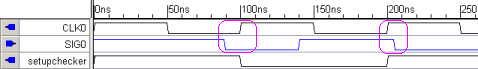

After simulation, the graphical waveform for the extra setup-checker signal will just be the output of the D flip-flop that was created when you entered the Boolean equation and the Clock Signal. Since this is not relevant to the continuous setup or hold check, you can, if you wish, hide the signal by selecting the signal name and choosing the View > Hide Signal menu.

The continuous setup or hold will cause messages to be sent to the Report Window simulation log tab. In the above diagram there is both a setup and hold error.