2.10 Debugging Transactor Clock Domains |

|

|

|

2.10 Debugging Transactor Clock Domains |

|

|

The most common problem with transactors is the accidental creation of a clock domain by putting a graphical construct such as a sample on the wrong clock edge while the rest of the transactor's objects are in another clock domain. Below are some ways of quickly checking on the clock domains.

Quick Check on the number of Clock Domains for each transactor

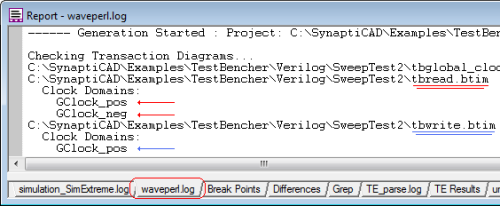

The waveperl.log file shows the names of the clock domains for each transactor in a project in one location. This display is useful to verify that transactors in a project are primarily operating within the same clock domain. Some additional clock domains may be employed by a particular transactor for checking purposes, but most of the transactors in a project TLM typically share a common clocking domain for synchronizing the application of stimulus waveforms to the models under test.

•Press the Make TB button to generate transactor code for each transaction timing diagram. |

|

•Look in the waveperl.log tab in the Report window to see the clock domains for each timing diagram. If you cannot see the Report window, choose the Window > Report menu to bring it to the front. |

Verifying Graphical Constructs are in proper Clock Domains

The comments at the top of each transactor's code quickly shows which signals and other graphical constructs are part of each clock domain. It's particularly important to verify graphical constructs are in the proper clock domain when time marker loops are used in a transactor (see below for more details).

•After generating the transactor code using the Make TB button as shown above, you can find the transactor code in the Project window under the Transaction Diagrams folder. •Double click on code file for each timing diagram to see the generated code in the Report window. |

|

•Read through the comments at the top of the transaction to see the clock domains and the objects they contain. •If you have a Loop within a transactor, then all graphical objects that occur within the loop interval should typically be in the same clock domain. For example, one common mistake would be to create a loop in a clock domain called GClock_pos, but trigger a sample or a setup contained in the loop's time interval on the negative edge of GClock (thereby placing the sample or setup in the GClock_neg clock domain). In this case, the sample or setup would only happen once rather than every iteration of the loop (which is probably not the intended operation). |

|