11.3 General GOF Information |

|

|

|

11.3 General GOF Information |

|

|

GOF's main purpose is to view and edit large Verilog netlists that have been generated from a synthesis or layout tool. Netlists sometimes require changes to either meet timing closure specifications, fix functional logic bugs, or to repartition a design. GOF with BugHunter allows GOF to also be used earlier in the design cycle. This section is just a little background on why you might want to use GOF in analyzing your backend design.

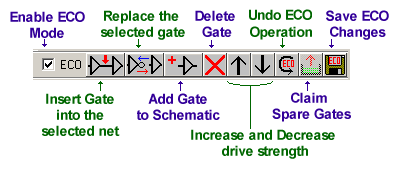

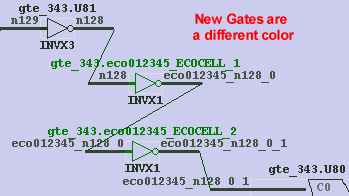

Using GOF, you can easily find and view specific logic cones in your design on a schematic to visualize just the paths you need to see without unnecessary clutter. GOF also simplifies mapping from RTL level constructs to their gate-level equivalents, so that you can pinpoint the locations where changes need to be made. GOF's ECO mode supports both graphical and script-based editing features for tracking ECO changes. Metal-only ECO operations are also supported with an automatic spare gates flow.