4.7 Simulator for Diagram Simulations |

|

|

|

4.7 Simulator for Diagram Simulations |

|

|

WaveFormer Pro's default behavior is to generate a Verilog model file and give it to a special version of SynaptiCAD's VeriLogger Pro to perform the simulation. The version of VeriLogger Pro that ships with WaveFormer is an interpreted simulator that is very fast at starting a simulation and finishing small simulation files. However, the simulator and the type of code generated can be changed.

•To change the generation language, use the drop-down on the button bar. If you choose VHDL, you must also provide a VHDL simulator so that the simulated signals work. |

|

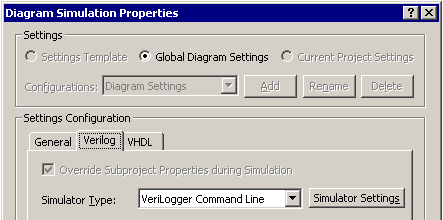

•To change the Simulator, press the Diagram Simulation Properties button to open the dialog. |

•Press the Verilog or VHDL tab, and choose a simulator from the Simulator Type box. •If you have never used the new simulator with WaveFormer, press the Simulator Settings button to open the Simulator / Compiler Settings dialog. |

•Use this dialog, to enter the path for the new simulator. |

|

Pre-Defined Environment Variable for Diagram Directory

There is a pre-defined environment variable that contains the directory where the currently simulating diagram is located. You can use this variable to make the diagram simulator search for library files in the diagram directory.

•Open the Diagram Simulation Properties dialog as shown above. •Add ;$(DiagramDir) to any path that you may want this directory searched, like the Library Directories box. |

;$(DiagramDir)

|