# Timing Diagram Editing and Analysis

Copyright © 2011, SynaptiCAD Sales, Inc.

# **Timing Diagram Editing and Analysis**

#### Copyright Copyright © 2011, SynaptiCAD Sales, Inc., version 14

All rights reserved. No parts of this work may be reproduced in any form or by any means - graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and retrieval systems - without the written permission of the publisher.

Products that are referred to in this document may be either trademarks and/or registered trademarks of the respective owners. The publisher and the author make no claim to these trademarks.

While every precaution has been taken in the preparation of this document, the publisher and the author assume no responsibility for errors or omissions, or for damages resulting from the use of information contained in this document or from the use of programs and source code that may accompany it. In no event shall the publisher and the author be liable for any loss of profit or any other commercial damage caused or alleged to have been caused directly or indirectly by this document.

Printed: January 2011 in (whereever you are located)

# **Timing Diagram Editing and Analysis**

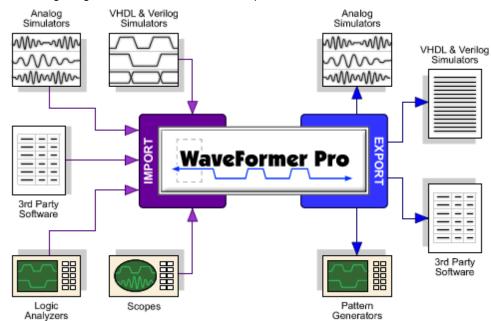

# DataSheet Pro, WaveFormer Pro, Timing Diagrammer Pro

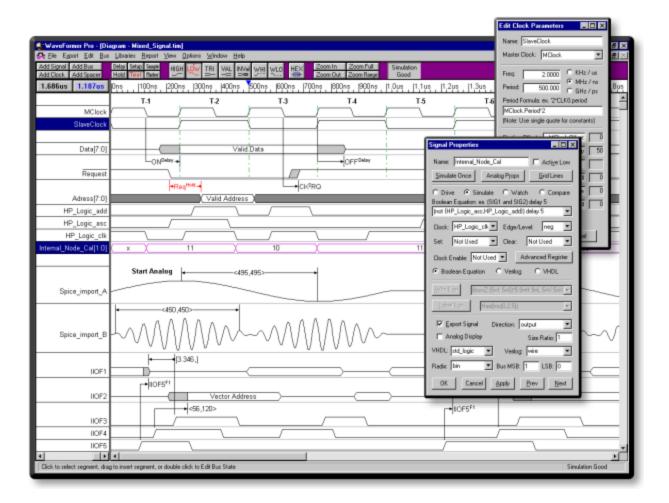

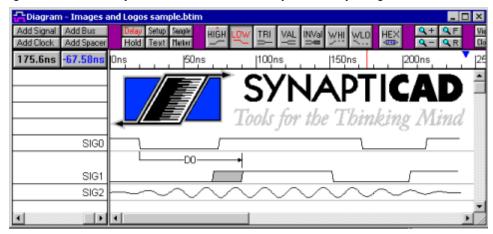

This is the manual for SynaptiCAD's timing diagram editing and analysis features. It is the main manual for WaveFormer Pro, Timing Diagrammer Pro, and DataSheet Pro. It is also a reference manual for the TestBencher Pro, VeriLogger, BugHunter, GigaWave and Transaction Tracker because these products also include some of the drawing and analysis features of the timing diagram editor.

# **Table of Contents**

# **Ultra-Quick Tutorial Chapter 1: Signals and Waveforms** 1.1 Adding Signals and Signal Properties...... 12

| 1.2 Drawing Waveforms                                 | 14 |

|-------------------------------------------------------|----|

| 1.3 Generating Waveforms and States with Equations    | 18 |

| 1.4 Colors, Line Type, Size, and More Visual Controls | 22 |

| 1.5 Measuring Time and State values                   | 26 |

| 1.6 Shifting, Clearing, and Moving Edges              | 30 |

| 1.7 Copy Signals or Waveforms                         | 31 |

| 1.8 Referencing Waveforms from Libraries              | 32 |

| 1.9 Hiding Signals                                    | 34 |

| 1.10 Base and Display Time Units                      | 36 |

| 1.11 Selecting, Moving, and Sorting Signals           | 36 |

# **Chapter 2: Clocks and Time Formulas**

| 3 | 9 |

|---|---|

| v |   |

51

59

8

12

| 39 |

|----|

| 43 |

| 44 |

| 46 |

| 47 |

|    |

# **Chapter 3: Buses and Differential Signals**

| 3.1 Virtual Buses                           | 51 |

|---------------------------------------------|----|

| 3.2 Group Buses                             | 53 |

| 3.3 Simulated Buses                         | 56 |

| 3.4 Differential Signals                    | 56 |

| 3.5 Converting Between Bus and Signal Types | 57 |

| 3.6 Symbolic State Names                    | 57 |

# **Chapter 4: Simulated Signals and VHDL/Verilog Export**

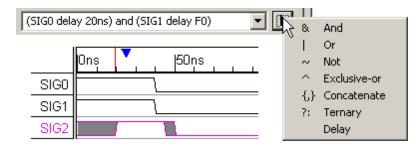

| 4.1 Boolean Equations with Delays        | 59 |

|------------------------------------------|----|

| 4.2 Register and Latch Equations         | 62 |

| 4.3 Direct Signal Code                   | 64 |

| 4.4 Export VHDL and Verilog test benches | 65 |

| 4.5 HDL Code Generation Settings         | 69 |

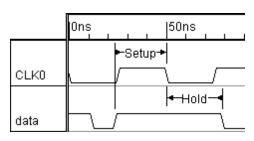

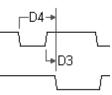

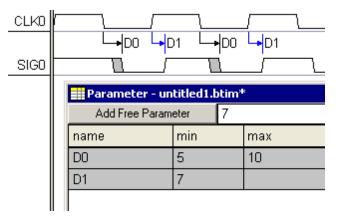

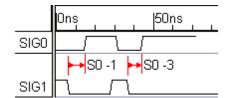

| Chapter 5: Delay, Setup, & Hold Parameters                 | 75  |

|------------------------------------------------------------|-----|

| 5.1 Delays                                                 |     |

| 5.2 Setups and Holds                                       | 79  |

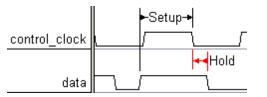

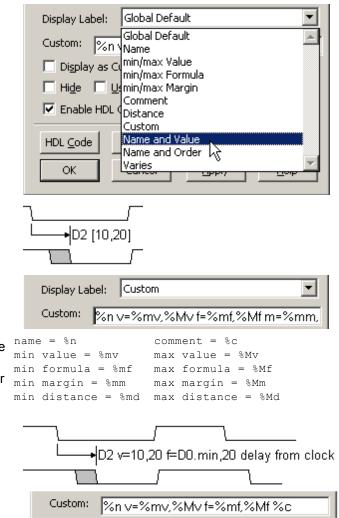

| 5.3 Display Settings for Parameters                        | 80  |

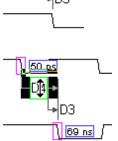

| 5.4 Drawing and Editing Parameters                         | 83  |

| 5.5 Hiding Parameters                                      | 84  |

| 5.6 Parameter Window                                       | 85  |

| 5.7 Time Formulas for Clocks and Parameters                | 88  |

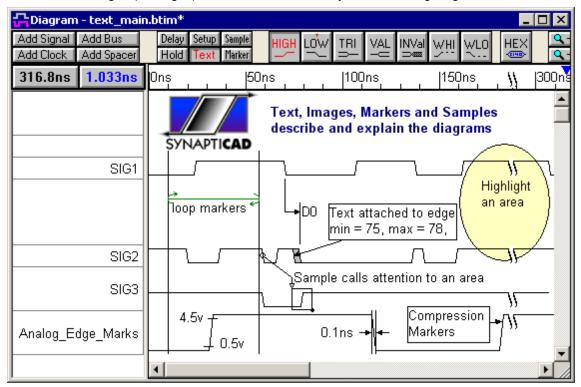

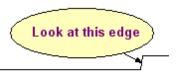

| Chapter 6: Text, Markers, and Samples                      | 91  |

| 6.1 Text                                                   | 91  |

| 6.2 Moving Text on the Alignment Grid                      |     |

| 6.3 Image and Logo Text Objects                            |     |

| 6.4 Highlight Areas with Text Objects                      |     |

| 6.5 Marker Lines                                           |     |

| 6.6 Samples                                                | 100 |

| 6.7 Japanese and other non-English Fonts                   | 101 |

| Chapter 7: Views, Images, and Printing                     | 103 |

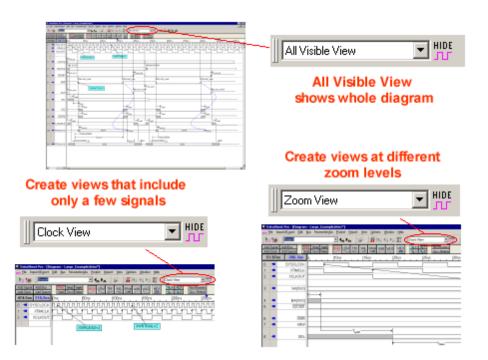

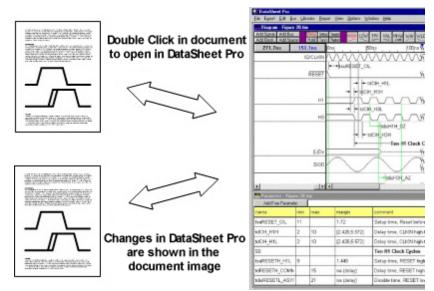

| 7.1 Views in DataSheet Pro                                 | 103 |

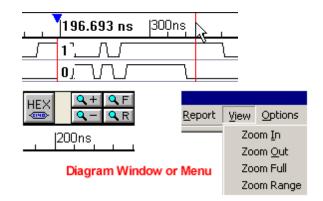

| 7.2 Zoom, Scroll, Search                                   | 105 |

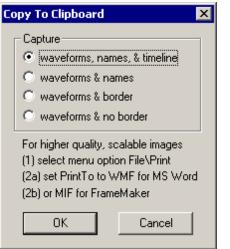

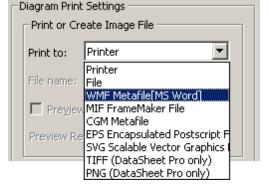

| 7.3 Images and Word Processors                             | 106 |

| 7.4 OLE- Object Linking and Embedding                      | 107 |

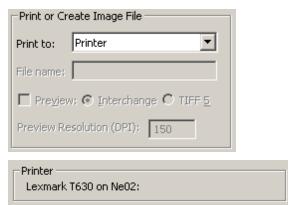

| 7.5 Printing                                               | 109 |

| 7.6 Miscellaneous Diagram Features                         | 111 |

| Chapter 8: Analog Display and SPICE                        | 115 |

| 8.1 Analog Waveform Display                                | 115 |

| 8.2 Waveform Equation Blocks for editable Analog waveforms | 116 |

| 8.3 Sine, Capacitor, Ramp & Exponential waveforms          | 120 |

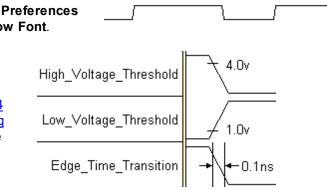

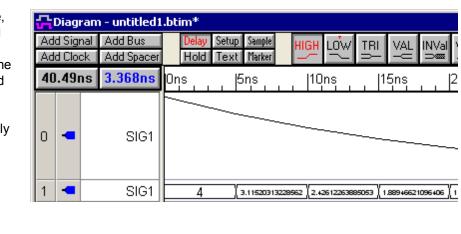

| 8.4 Display Edge Switching Thresholds                      | 123 |

| 8.5 Exporting SPICE Stimulus                               |     |

| 8.6 Importing SPICE waveforms                              |     |

| 8.7 Changing the Sampling Frequency of Waveforms           | 127 |

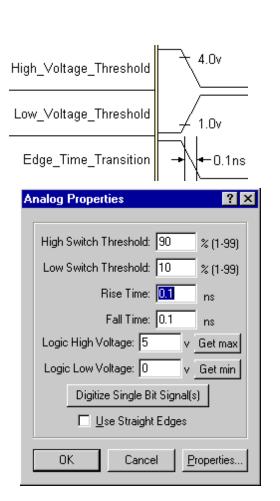

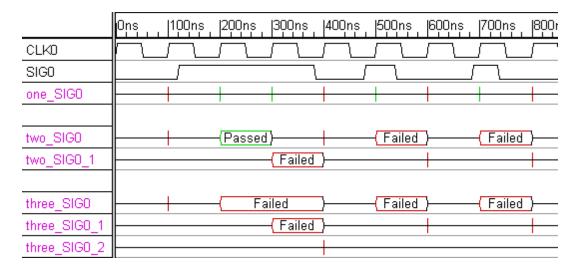

| Chapter 9: Compare and Transaction Tracker Options         | 129 |

| 9.1 Performing a Signal Compare                            |     |

| 9.2 Viewing Compare Differences                            |     |

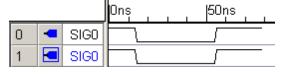

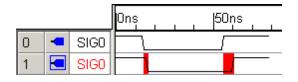

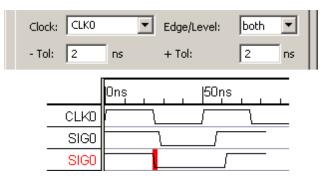

| 9.3 Tolerance, Clocked, and Don't Care                     | 133 |

Timing Diagram Editing and Analysis

| 9.4 Transaction Tracker                                | 134 |

|--------------------------------------------------------|-----|

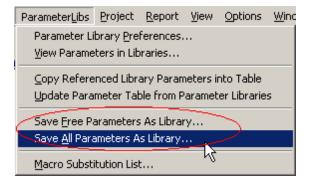

| Chapter 10: Parameter Libraries and Merging Diagrams   | 138 |

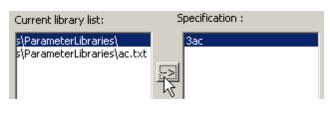

| 10.1 Adding Libraries, Specifications, and Macros      | 138 |

| 10.2 Referencing and Viewing Library Parameters        | 140 |

| 10.3 Making Parameter Libraries                        |     |

| 10.4 Merging Diagrams                                  | 144 |

| 10.5 Self-Contained Timing Diagrams                    | 146 |

| Chapter 11: Simulator and Test Equipment Support       | 148 |

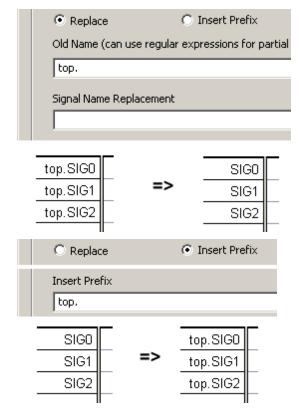

| 11.1 Signal Names for export and import                | 149 |

| 11.2 Import General Instructions                       | 150 |

| 11.3 Export General Instructions                       | 154 |

| 11.4 Map Signals to Test Equipment Pins                | 157 |

| 11.5 Batch Mode                                        | 159 |

| 11.6 Agilent Logic Analyzer & Oscilloscope - Import    | 165 |

| 11.7 Agilent Pattern Generator - Export and Import     | 168 |

| 11.8 Agilent and HP file transfer instructions         | 169 |

| 11.9 ALTERA Max Plus II Simulator - Export             | 170 |

| 11.10 Pulse Instruments Pattern Generator - Export     | 171 |

| 11.11 Spreadsheets - Import and Export                 | 173 |

| 11.12 STIL Test Vectors - Export                       | 175 |

| 11.13 TDML Support - Import and Export                 | 176 |

| 11.14 Tektronix Logic Analyzer & Oscilloscope - Import | 177 |

| 11.15 Tektronix Pattern Generator - Export             |     |

|                                                        |     |

# Appendix A: Menus and Colors

| 1 | 8 | 1 |

|---|---|---|

|   | v |   |

| File Menu           |                             | 181 |

|---------------------|-----------------------------|-----|

| Import/Export       | Menu                        | 182 |

| Edit Menu           |                             | 183 |

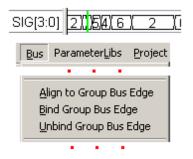

| Bus Menu            |                             |     |

| ParameterLib        | s Menu                      | 185 |

| Project Menu        |                             | 186 |

| Report Menu         |                             | 186 |

| View Menu           |                             |     |

| <b>Options Menu</b> |                             |     |

| Window Menu         |                             |     |

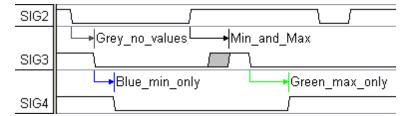

| Colors and the      | eir Significance            | 189 |

| Appendix E          | 3: Writing Waveperl Scripts | 191 |

| B.1 What is Perl? |

|-------------------|

|-------------------|

|                                                             | Contents | 7   |

|-------------------------------------------------------------|----------|-----|

|                                                             | L        |     |

| B.2 Perl Data Types                                         |          | 192 |

| B.3 Pattern Matching (Regular Expressions)                  |          | 193 |

| B.4 Notes on Writing Import/Export Scripts                  |          | 194 |

| B.5 Object Properties                                       |          | 195 |

| B.6 Adding New Scripts                                      |          | 196 |

| Appendix C: WaveFormer Lite Help                            |          | 198 |

| C.1 WaveFormer Lite Design Flow                             |          | 198 |

| C.2 WaveFormer Purchasing Options                           |          | 199 |

| C.3 Specifying Signal Types for Actel Fusion Analog Signals |          | 201 |

| C.4 Compiling Latest ModelSim Libraries                     |          | 202 |

# Index

# **Ultra-Quick Tutorial**

This Ultra Quick tutorial shows you how to draw a simple timing diagram and simulate a simple Boolean equation. More comprehensive tutorials are available from the **Help > Tutorials** menu.

| 🕂 Diagram - untit                     | led1.b | tim*          |               |     |                     |     |          |      |             |          |    |     | _ [       | ⊐ ×                                  |

|---------------------------------------|--------|---------------|---------------|-----|---------------------|-----|----------|------|-------------|----------|----|-----|-----------|--------------------------------------|

| Add Signal Add Bu<br>Add Clock Add Sp |        | Delay<br>Hold | Setup<br>Text | _   | ні <mark>с</mark> н | ιow |          |      | INVal<br>⊃œ | МĦ       |    | HEX |           | <mark>૧</mark> +<br><mark>૧</mark> - |

| 350.0ns 100.0                         | Ins C  | Ins           |               | 100 | )ns                 | I   | 200r     | ıs 🔽 | 1 1         | 300j     | ns | 1 1 | 400       | ns                                   |

| CL                                    | ко Г   |               | 1             |     |                     |     | <u> </u> |      |             | <u>_</u> | Į. | •   | <u></u>   | -                                    |

|                                       |        |               |               | 0   |                     |     |          |      |             |          |    |     |           |                                      |

| SI                                    | IGO 🗌  |               | Π             |     |                     |     |          |      | 1           |          |    |     | $\square$ |                                      |

| S                                     | G1     |               |               |     |                     |     |          |      |             |          |    | 1   |           | _                                    |

| •                                     |        | (             |               |     |                     |     |          |      |             |          |    |     |           | •                                    |

#### 1) Open a new timing diagram file

Choose File > New Timing Diagram menu to open an new timing diagram.

| 유Diagram - untitled1.btim |            |    |          |       |        |     |  |

|---------------------------|------------|----|----------|-------|--------|-----|--|

| Add Signal                | Add Bus    |    | Delay    | Setup | Sample |     |  |

| Add Clock                 | Add Spacer |    | Hold     | Text  | Marker |     |  |

| 95.23ns                   | 95.23ns    | On | s<br>I I |       | 50     | )ns |  |

|                           |            |    |          |       |        |     |  |

|                           |            |    |          |       |        |     |  |

#### 2) Add a clock with a period of 100 ns

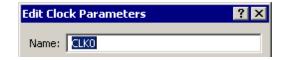

- Press the **Add Clock** button to open the *Edit Clock Parameters* dialog.

- The default period is already set to 100 ns, so the clock is created. However, notice that the clock can also be defined using a reference clock or a period formula. <u>Chapter 2: Clocks</u> 39 covers these options in

- Press **Ok** to close the dialog.

more detail.

| Add Signal | Add Bus    |

|------------|------------|

| Add Clock  | Add Spacer |

| Edit Cloc | k Parameters           | ? ×        |

|-----------|------------------------|------------|

| Name:     | CLKO                   |            |

| Referen   | ce Clk: None           | •          |

| Freq:     | 10.                    | C KHz / us |

| Period:   | 100.                   | -          |

|           | ormula: ex. 2*CLK0.per | riod       |

| 100       |                        |            |

| Starting  | Offset:                | 0 0        |

| Duty Cy   | de %:                  | 50 50      |

9

#### 3) Add SIG0 and draw its waveform

- Click the Add Signal button to add a blank signal with the default name of SIG0.

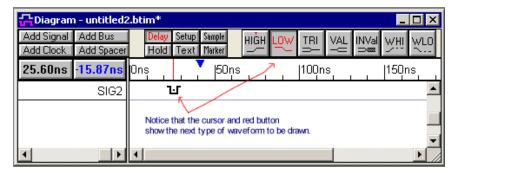

- Look at the waveform buttons. The red one controls the type of waveform that is drawn next. After that the buttons will toggle to the state with the red T on top. Pressing the buttons will set a different draw and next state. This shows a toggling between high and low states.

| Add 9    | Signal ( | Add E | 3us 🗌  |             |    |     |

|----------|----------|-------|--------|-------------|----|-----|

| Add (    | Clock (  | Add 9 | òpacer |             |    |     |

|          |          |       |        |             |    |     |

| HIGH     |          |       |        | INVal<br>⊃‱ | ΜШ | WLO |

| <u> </u> |          |       |        |             | -  | N   |

• Put the mouse cursor on the same row as the signal **SIG0** at about **100ns** and **left click** to draw a high waveform from 0ns to the mouse cursor position. Move the cursor to **150ns** and **click** the mouse button to draw a low segment from the end of the signal to the cursor point. Draw some more segments on SIG0 while watching the waveform buttons. <u>Chapter 1: Signals and Waveforms</u> 12 covers all of the signal drawing and display features.

| <b>G</b> Diagram | - untitled1 | .bti | m*       |       |        |            |        |               |             |          |      |               |          |

|------------------|-------------|------|----------|-------|--------|------------|--------|---------------|-------------|----------|------|---------------|----------|

| Add Signal       |             |      | Delay    | Setup | _      | HIGH       | LOW    | TRI           | VAL         | INVal    | WHI  | WLO           | HEX      |

| Add Clock        | Add Spacer  |      | Hold     | Text  | Marker | <u> </u>   | $\sim$ | $\rightarrow$ | $- \square$ |          | Z    | $\sim \cdots$ | -        |

| 393.2ns          | 18.43ns     | On   | s<br>I I | 1     | ,  100 | ns         | 1      | 200 r         | IS          |          | 300ı | ns            |          |

|                  | CLKO        |      |          | L     |        |            |        | <u> </u>      |             |          |      |               | /        |

|                  | SIGO        |      |          |       |        |            | Z      |               | . <u> </u>  | <u> </u> |      |               | <u>-</u> |

|                  |             |      |          |       |        | $\times$ / | 1      |               |             |          |      |               |          |

|                  |             |      |          |       | left o | click      | in tl  | hese          | e pla       | aces     | 5    |               |          |

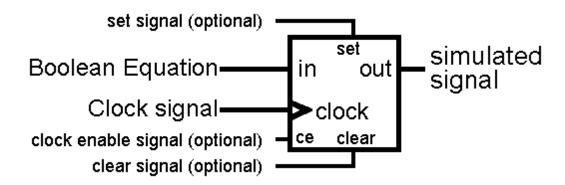

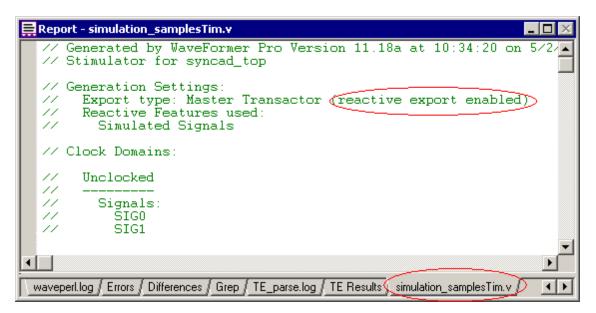

#### 4) Add signal SIG1 and simulate it as the a Boolean equation of SIG0 and CLK0

This step requires at least WaveFormer Pro. If you are using Timing Diagrammer skip to the next step.

- Click the Add Signal button to add a signal, then double click on the SIG1 name to open the Signal Properties dialog. This dialog allows the name and other signal properties to be changed.

- Enter the equation **SIG0 and CLK0** into the Boolean Equation edit box. The signal names are case sensitive.

- Select the **Simulate** radio button. This setting automatically re-simulates SIG1 whenever an input waveform is changed.

- Click **OK** to close the dialog.

| Signal Properties 🛛 ? 🗙                         |

|-------------------------------------------------|

| Name: SIG1 Contractive Low                      |

| Simulate Once Analog Props Grid Lines           |

| O Drive O Simulate O Watch O Compare            |

| Equation Entry Verilog VHDL                     |

| Type: Boolean Eqn 💌 ex. (SIG1 and SIG2) delay 5 |

| SIGO and CLKO                                   |

| Clock: Unclocked 💌 Edge/Level: pos 💌            |

| Set: Not Used 💌 Clear: Not Used 💌               |

| Clock Enable: Not Used 💌 Advanced Register      |

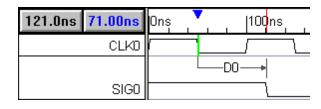

Experiment with the simulated signal by dragging and dropping an edge on SIGO. Each time the edge is moved, a simulation is performed and SIG1 redraws itself. (The clock edges cannot be moved with the mouse).

| 121.0ns | 168.0ps | Ons  100ns | 200 <sub>1</sub> r |

|---------|---------|------------|--------------------|

|         | CLKO    |            |                    |

|         | SIGO    |            |                    |

|         | SIG1    |            |                    |

• Add a 10ns delay to the SIG1 equation by changing the equation to (SIG0 and CLK0) delay 10. Verify that SIG1 is correctly drawn. <u>Chapter 4: Simulated Signals</u> solution.

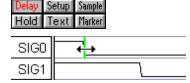

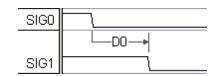

#### 5) Add a delay parameter named D0.

- Press the **Delay** button so that right clicks will add delays.

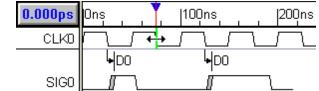

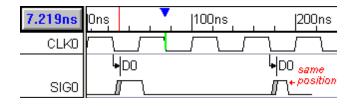

- Left click on the falling edge of CLKO at 50ns to select the edge, then Right click on SIG0's *first transition* (at about 100ns). This draws a delay parameter from the selected clock edge to the SIG0 edge.

- Double-click on **D0** to open the *Delay Properties* dialog.

- Enter **15** into the **Min** box, and **25** into the **Max** box, then press **OK** to close the dialog.

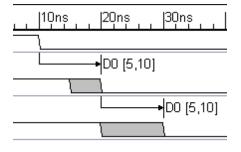

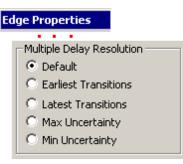

- Notice that the SIG0 transition has moved so that it starts 15ns from the clock edge and the gray uncertainty region is 10ns wide (25-15=10). <u>Chapter 5: Delay, Setup, &</u> <u>Hold Parameters</u> 75 covers parameters in more detail.

| Delay | Setup | Sample |

|-------|-------|--------|

| Hold  | Text  | Marker |

| Delay Pr | operties                             | _ 🗆 🗵 |

|----------|--------------------------------------|-------|

| Name:    | DO                                   |       |

| Min:     | 15                                   | 15    |

| Max:     | 25                                   | 25    |

|          | 434.2ns Ons 100<br>CLK0 D0<br>SIG0 1 | ns    |

#### Summary

Congratulations you have completed the Ultra-Quick Tutorial. The Tutorial covered starting an new timing diagram, generating a clock, drawing a signal, simulating a signal, and adding a delay parameter. In general, the following mouse functions are used in the program:

- Left mouse click to draw waveforms and move things around.

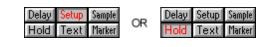

- **Right mouse** click to add the object highlighted in second group of buttons on button bar (like adding delays or text).

| Delay | Setup | Sample |

|-------|-------|--------|

| Hold  | Text  | Marker |

• **Double-click** on objects to edit them (like signal names, text objects, parameters, edges, clocks).

Please take the time to look through the manual to get an idea of the timing analysis and display features that are not covered in the Ultra-Quick Tutorial. Also the **Help > Tutorials** menu has much longer and in depth tutorials.

# **Chapter 1: Signals and Waveforms**

This chapter covers how to add basic signals, draw the waveforms for the signals, and how to manage the display and navigate through large numbers of signals.

| <mark>∰</mark> Diagram - signals_i         | main.btim                                                                                                                         |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Add Signal Add Bus<br>Add Clock Add Spacer | Delay     Setup     Sample       High     LOW     TRI     VAL     INVal     WHI     WLO       Hold     Text     Marker     Marker |

| 160.3ns 71.17ns                            | 0ns50ns100ns150ns                                                                                                                 |

| SIGO                                       | Draw high/low waveforms and weak high/low waveforms                                                                               |

| SIG1[7:0]                                  | (                                                                                                                                 |

|                                            | Generate signals using label and waveform equations<br>Attach full and partial Gridlines                                          |

| SIG2                                       |                                                                                                                                   |

| ColorFullSignals                           | Change Color, Size,<br>and Line type control                                                                                      |

|                                            |                                                                                                                                   |

Later chapters cover more advanced signal types, which calculate their own waveforms or display specialized information:

- Clocks, repetitive waveforms are drawn automatically, are covered in Chapter 2: Clocks 391.

- Buses and Differential Signals, multi-bit signals, are covered in Chapter 3: Buses 51.

- **Simulated Signals** which calculate their waveforms based on Boolean equations, registered logic, and behavioral HDL code are covered in <u>Chapter 4: Simulated Signals</u> [59].

## **1.1 Adding Signals and Signal Properties**

Signals can quickly be added using the the appropriate button below. Double clicking on the name of a signal opens the *Signal Properties* dialog which sets the properties for a specific signal including it's name, export type, display features and whether or not the waveform is generated by a Boolean equation. This dialog can also edit several signals simultaneously.

To add a new signal:

| <ul> <li>Click the Add Signal button.</li> </ul> | Add Signal | Add Bus   |

|--------------------------------------------------|------------|-----------|

|                                                  | Add Clock  | Add Snace |

• Note: The above buttons are located in a timing diagram window. You can open a new timing diagram window using the **File > New Timing Diagram** menu.

#### Edit a signal's name and other properties:

- Double-click on a *signal name* to open the *Signal Properties* dialog and type in a new name.

- Active Low signals are displayed with a bar (line) drawn over the top of the name. In equations, active low signals are referred to as *name*\$BAR.

| Signal Pr     | operties |        |                     | ? ×                |

|---------------|----------|--------|---------------------|--------------------|

| Name:         | SIGO     |        | Acti <u>v</u> e Low |                    |

| Simulate Once |          | Analog | g P <u>r</u> ops    | <u>G</u> rid Lines |

| O Driv        | O Si     | mulate | O Watch             | C Compare          |

- Drive is the default state used for drawn signals and is the most common signal state for signals in a timing diagram. The other states are used by special features: Simulate is for creating continuously simulated signals (see Section 4.1: Boolean Equations with Delays [59]), Compare is for waveform comparison signals (see Section 9.1: Performing a Signal Compare [130]), and Watch is used by the BugHunter environment for watching signals in a simulation (see Section 2.2: Watching Signal and Component Waveforms in the BugHunter manual for more information).

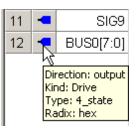

- **Radix** determines the base in which signal values are displayed.

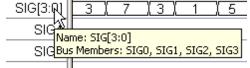

- **Bus MSB** and **LSB** determines the bit size of the signal. A single bit signal is (0,0). <u>Chapter 3</u> 51 covers buses and differential signals.

- Direction sets the port direction of the signal relative to the testbench. Output signals drive the model under test. Input signals represent signals with data coming back from the model under test. Internal signals are signals that are not connected to the ports of the model under test. The direction is also shown as an icon to the left of the signal name in the label window. To turn off this column choose the Options > Draw Preferences menu and uncheck the Show Direction Icons box.

- A quick way to view a signal's properties is to put the mouse over the direction column and a tooltip will appear. Placing the mouse over the signal's name shows a tooltip of the full signal name, which is handy for signals with long names.

| 0 | - | output_sig   |

|---|---|--------------|

| 1 |   | input_sig    |

| 2 | + | inout_sig    |

| 3 | Л | internal_sig |

**Signal Name Rules:** Normally spaces are not allowed in signal names. For documentation purposes, you can get spaces into a signal name by using the **Edit > Search and Rename** menu. However, adding spaces to signal names may cause problems when exporting to different formats or simulating Boolean Equations. Signal names beginning with "\$\$" are reserved for internal use. Signal names should not be the same as common Boolean operators (examples: AND, OR), if you plan to

export to VHDL.

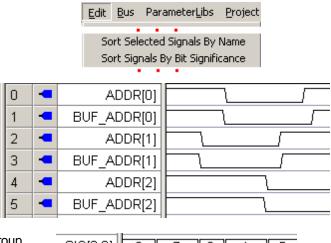

#### To move or sort signals:

<u>Section 1.11: Selecting. Moving. and Sorting Signals</u> <sup>36</sup> describes several techniques for moving signals with the mouse or sorting them into a particular order. The easiest way to move a signal is to select the signal label and drag it using the mouse. Also, the Edit > Sort Signals By Name menu will rearrange signals in alphabetical order.

#### To delete a signal or multiple signals:

Click on one or more *signal names* to highlight the names and then press the **Delete** key. When a signal is deleted, any parameters or text connected to it are also deleted. The **Edit** > **Undo** or **Edit** > **Undo Delete** menu item will undo a mistaken delete.

#### Change the Auto Name generation:

• By default, signals are named SIG# but the "SIG" prefix can be changed by right clicking on the **Add Signal** button to open the *Modify Auto Signal Name Prefix* dialog and entering a new prefix. Bus and Clock prefix names work the same way.

# **1.2 Drawing Waveforms**

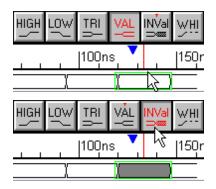

The timing diagram editor is always in drawing mode so left clicking on a signal will draw a waveform. The red state button controls the type of waveform that is drawn (high, low, tri-state, valid, invalid, weak high, and weak low). The buttons toggle back an forth between two states, and the next state is indicated by the little red T on top. Click on the state buttons to set the toggle and next state.

#### To draw the waveform of a signal:

• Place the mouse cursor inside the *Diagram* window at the same vertical row as the signal name. The red state button on the button bar determines the type of waveform drawn. The cursor shape also mirrors the red state button.

Click the left mouse button. This draws a waveform from the end of the signal to the mouse cursor.

| t      | Add Signal | Add Bus    | Delay | Setup | Sample | HIGH | เก๋พ | TBL   | VAL  | INVal | MH   |

|--------|------------|------------|-------|-------|--------|------|------|-------|------|-------|------|

| on.    | Add Clock  | Add Spacer | Hold  | Text  | Marker | 1    | 2    | ÷h    | Ϋ́   |       | 211  |

| a<br>m | 73.73ns    | 48.13ns    | Ons   | ▼     | 50ns   |      | 1    | 100 n | s, i | 1     | 150r |

| ie     |            | SIG2       |       | _     |        | л    |      |       |      |       |      |

|        |            |            |       |       |        |      |      |       |      |       |      |

TRI

VAL

HIĠH

Move the mouse to the right and click again to draw another segment.

Add Signal

Add Bus

Add Clock Add Spacer

• Keep drawing from left to right across the diagram.

| k<br>/ | 99.3ns        | 7.680ns | Ons   | 50           | ns | T 100ns | 3 | 150n |

|--------|---------------|---------|-------|--------------|----|---------|---|------|

|        |               | SIG2    |       |              |    | ប       |   |      |

|        |               |         |       |              |    |         |   |      |

| r      | A 44 Cianal I | A 44 D  | Dalau | Cabor County |    | • I     | _ | _    |

Hold Text Marker

- g

Add Signal

Add Bus

Delay

Setup

Sample

HIGH

LOW

TRI

VAL

INVal

WHI

Add Clock

Add Spacer

Hold

Text

Marker

HIGH

LOW

TRI

VAL

INVal

WHI

99.00ns

0.000ps

Ons

150ns

100ns

150r

SIG2

- Pressing the middle mouse button either toggles the state buttons or cycles through them depending on the setting in the *General Preferences* dialog. Choose Options > General Preferences menu to open the dialog.

There are several mouse-based editing techniques used to modify existing waveforms. These techniques will only work on signals that are drawn. They will not work on generated signals like clocks and simulated (blue) signals that are covered in later chapters.

#### 1) Drag-and-Drop a Signal Transitions:

- To move one transition, click on the transition and drag it to the desired location.

- To move all of the transitions on one signal, hold down the <1> and <2> number keys while dragging. Holding down just the <1> key moves all the edges to the left, and the <2> key moves all the right.

- To move transitions on different signals, first select the transitions by holding the

<CTRL> while clicking on them. Then select and drag on the final selected edge to move all the selected transitions an equal distance in time.

#### 2) Click-and-Drag to insert a segment into a waveform:

- Inside of a segment, click and drag the cursor to insert a segment

- The inserted state is determined by the red state button

#### 3) Change a segment's graphical state by selecting it and then pressing a state button:

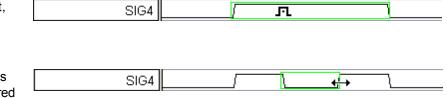

- Click in the middle of the segment to select it (so that it has a green box around it).

- Click on a state button to apply that graphical state to the segment. If you change a segment to same level as an adjacent section, the transition will turn red to preserve the edge data. This transition can be deleted if necessary.

#### 4) Adding virtual state Information to a segment

Chapter 3.1: Virtual Buses 51 covers all of details of Virtual states on buses.

• For Signals, double-click on the middle of a segment to open the *Edit Bus State* dialog, and then type in a new value into the **Virtual** edit box.

• For Clocks, press the **Hex** button and then double-click on the middle of the segment to open the *Edit Bust State* dialog. If the Hex button is not pressed, the double-click will open a different dialog to allow editing of the clock.

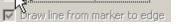

#### 5) Making Waveforms end at a common time

• Sketch waveforms, then press the **Marker** button down.

| ٠ | Right click in the diagram     |

|---|--------------------------------|

|   | window past the ends of the    |

|   | waveforms to add a time marker |

|   | line.                          |

| <b></b> Diagran | n - untitledu  | J.btim*                                   |         |        |      |   |

|-----------------|----------------|-------------------------------------------|---------|--------|------|---|

| Add Signal      | Add Bus        | Delay                                     | Setup   | Sample | HIGH | ſ |

| Add Clock       | Add Spacer     | Hold                                      | Text    | Marker |      |   |

| 58.88ns         | -24.06ns       | Ons                                       |         | 50h    | s ,  |   |

|                 | SIGO           |                                           |         |        |      |   |

|                 | SIG1           |                                           |         |        |      |   |

|                 | SIG2           |                                           |         |        |      |   |

|                 |                |                                           |         |        |      |   |

| 56.83ns         | Onș , ,        | ,  50r                                    | ns ,    |        | 10   |   |

|                 |                |                                           |         | MAR    | KD   |   |

| SIGO            |                | 1                                         | <u></u> |        |      |   |

| SIG1            |                |                                           |         |        |      |   |

| SIG2            |                | $ \  \  \  \  \  \  \  \  \  \  \  \  \ $ |         |        |      |   |

|                 |                |                                           |         |        |      |   |

| 🔹 🔽 🖓 Signal e  | ends snap to r | narkeri                                   |         |        |      |   |

• Double-click on the time marker line to open the *Edit Time Mark er* dialog, and check the **Signal ends snap to marker** control.

Note that the waveforms snap to the marker, but are not truncated. All signal transitions remain intact, even if the marker is moved. Only the last segment of the signal ends at the marker

| -10.65ns | Ons | 🕴  100ns |

|----------|-----|----------|

|          |     | MARKO    |

| SIGO     |     |          |

| SIG1     |     |          |

| SIG2     |     | <b>→</b> |

#### 5) Adjusting the drawing Grid

Drawn signals transitions are automatically aligned to the closest grid time. The grid does not affect the placement of edges that are moved by delays or formulas. By default the grid is set to the base time unit, because this generates nice VHDL and Verilog stimulus generation files with whole number times (like 2ns instead of 2.465ns). Sometimes it is convenient to set the grid to a multiple of the clock frequency to make all new signal edges line up with the clock edges.

- Choose the **Options** > **Text and Edge Grid Settings** menu item to open the *Edit Text and Edge Grids* dialog.

- The **Signal Edge Grid** section controls where the waveform edges will be placed on the **Horizontial** grid.

- The Enforce as Sampling Period control is used by the Analog State Label equations and does not effect the drawing of signals (see Section 8.3: Sine, Capacitor, Ramp & Exponential waveforms [120]). A newer method of generating analog waveforms that are editable as equations are described in Section 8.2: Waveform Equation Blocks for editable Analog waveforms [116].

| Options   | <u>W</u> indow    | <u>H</u> elp |                  |     |

|-----------|-------------------|--------------|------------------|-----|

| Text a    | ind Edge <u>G</u> | rid Settings |                  |     |

| Edit Text | t and Edg         | e Grids      |                  | ? × |

| Defaul    |                   | Diagram      |                  | 1   |

| Sign      | al Edge Gri       | id           |                  |     |

|           |                   | Sampling P   | eriod<br><br>_ps |     |

|           |                   |              |                  |     |

#### 7) Snap signal transitions to the closest clock edge

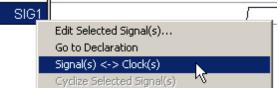

A quick way to line up the edges of signal is to snap them to the previous clock edge using the **Cyclize Selected Signal(s)** context menu.

- Sketch a waveform that is close to lining up with a clock.

- Setup the signal's clocking signal, by double clicking on the signal name to open the Signal Properties dialog, and set he clocking signal using the Clock box and set the Edge/Level to both (or just neg or pos if you only want to snap to those edges).

| CLKO   |      |   |             |      |   |   |

|--------|------|---|-------------|------|---|---|

| SIG5   |      |   |             |      |   | • |

| Clock: | CLK0 | • | Edge/Level: | both | • |   |

- Right-click on the signal name and choose Cyclize Selected Signal(s) from the context menu.

- Notice that the edges are lined up with the clock edges

|                            | CLKO |   | <u>_</u> |

|----------------------------|------|---|----------|

|                            | SIG5 |   | ٦        |

| Edit Selected Signal(s)    |      | F |          |

| Go to Declaration          |      |   |          |

| Signal(s) <-> Clock(s)     |      |   |          |

| Cyclize Selected Signal(s) |      |   |          |

| Hide Selected anal(s)      |      |   |          |

| сько стра                  |      |   |          |

| SIG5                       |      |   |          |

- 8) Finding the exact edge time and locking the edge

- Double-click on an edge of the signal transition to open the *Edge Properties* dialog.

<u>Section 1.5</u> 26 discusses timing analysis features of this dialog.

- To move an edge, enter a new **min** or **max** time.

- To lock an edge so that it cannot be moved, check the **Locked** checkbox.

| E | Edge Properties    |   |  |  |  |  |

|---|--------------------|---|--|--|--|--|

|   | Edge Placement     | 1 |  |  |  |  |

|   | Min: 50            |   |  |  |  |  |

|   | Max: 50            |   |  |  |  |  |

|   | Min Uncertainty: 0 |   |  |  |  |  |

|   | Uncertainty =0 ns  |   |  |  |  |  |

|   | 🔲 Locked           |   |  |  |  |  |

|   |                    |   |  |  |  |  |

• Note: All edges on a signal can be locked by selecting the signal name, and then choosing the Edit > (Un)Lock Edges of Selected Signals from the main menu.

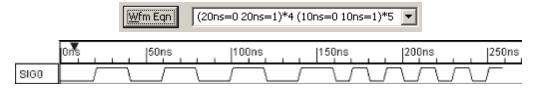

# **1.3 Generating Waveforms and States with Equations**

Waveforms can be generated from Waveform Equations and automatically labeled using State Label equations. These features provide a quick way to generate signals that have a known pattern that is more complicated than a periodic clock cycle. The label equations also provide a quick way to define analog data for a waveform.

This is an older method of generating waveform data and these equations generate "one-time" results (the generated events react thereafter the same as if you had manually drawn these events). A newer method called Waveform Equation Blocks preserves the original equation for subsequent editing. These are described in <u>Section 8.2</u>: Waveform Equation Blocks for editable Analog waveforms [116].

#### To apply a Waveform or Label Equation to a signal:

• Double-click on a signal's name to open the *Signal Properties* dialog.

| <u>₩</u> fm Eqn | 8ns=Z (5=1 5=0)*5 9=H 9=L 5=V 5=X | • |

|-----------------|-----------------------------------|---|

| Label Eqn       | Hex(Inc(0,2,5))                   | ► |

- Enter an equation and press the **Wfm Eqn** or **Label Eqn** button to apply it.

- The drop-down boxes have example equations and a history of past equations that you can modify so that you do not have to memorize the syntax. The black triangle is a quick add box that will enter the function values into the box.

#### **Rules for Waveform Equations:**

Each time you press **Wfm Eqn** button the waveform equation will be appended to the end of the signal, so you can build up a waveform using several smaller equations. The following example, uses a waveform equation to generate a variable frequency clock that switches from 25Mhz to 50Mhz. The initial frequency of 25MHz (period = 20+20 = 40ns) for 4 cycles and switches to 50Mhz for 5 more cycles. This type of waveform is tedious to draw by hand, but can be concisely expressed as a waveform equation. Pressing the button again would apply another set of waveforms to the end of the signal.

- A Waveform equation is a list of *space-separated*, time-value pairs in the form **TimeValue** [units]=StateValue or **TimeValue=StateValue**.

- If [units] are not specified, then the "display time unit" of the current project will be used.

- Legal graphical **StateValues** are: 0 = strong low, 1= strong high, Z = tristate, V = valid, X = invalid, L = weak low, and H = weak high.

- If the **StateValue** is not a graphical state, then a valid segment will be created and labeled with the state value. This allows you to label a signal with bus values and symbolic names while using the Waveform Equations. For example, **10ns=hello** will draw a 10ns long valid segment with a state value of *hello*.

- For loops, enclose a list of time-value pairs in *parenthesis* followed by a *multiply symbol* and the number of times the list is to be repeated.

- The default waveform equation contains all of the available states and syntax, so If you start by editing the default equation then you do not have to memorize the waveform equation rules.

#### **Rules for Label Equations:**

Each time you press the **Label Eqn** button the old state values are discarded and the new ones are written in (unlike the waveform equations which append to the end). Label equations provide a quick way to enter state values into digital counter signals and analog sine and capacitor discharge signals. For example a simple counter that starts at one and counts to ten could be written as: skip(3), inc(1,1,10). This tells the program to skip three segments, then to start labeling at one and place ten labels, incrementing by one each time. Functions can be combined by using a **comma** between the commands.

- The black triangle to the right of the box is a quick fill box that will enter an equation into the state label box. Then all you have to do is replace the variables with your values.

- Tip: First use a Waveform Equation to create an unlabeled signal with the correct number of segments, and then label it with a State Label Equation. For example (20=V)\*100 creates a waveform with 100 valid segments that are 20ns wide.

- A Label equation is a comma separated list of label functions.

- The label functions are applied in the order listed.

- Each label function returns a value of **list** so whenever you see **list** you can use a function, a single value like 5 or blue, or a list in parentheses (2,3,4).

```

appl

, (Concatenate)

Inc(start,increment,count)

Dec(start, decrement, count)

IncString("string", start, increment, count)

Range(start,finish,count)

RandInt(count, Range_to_zero)

Hex(list)

Bin(list)

Rep((list), count)

Skip(count)

dt.

File("filename.txt")

Signal("signalname")

map {operations} list

PRBS7(length,seed)

PRBS15(length,seed)

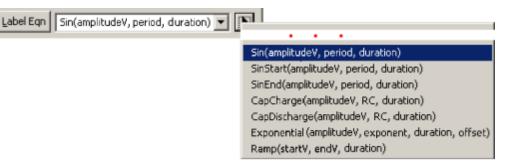

Sin(amplitudeV, period, duration)

SinStart(amplitudeV, period, duration)

SinEnd(amplitudeV, period, duration)

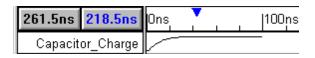

CapCharge(amplitudeV, RC, duration)

CapDischarge(amplitudeV, RC, duration)

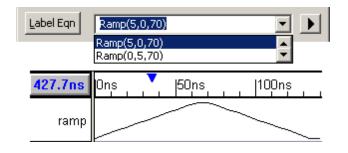

Ramp(StartV,EndV,Duration)

```

#### Digital state label functions

#### Inc(start, increment, count)

This function generates labels that begin at **start** and increase by **increment** each time. A total of **count** labels will be generated. The actual labels generated will be *start*, *start* + *increment*, *start* + *(increment \* 2)*, ..., *start* + *increment \* (count - 1)*.

| Inc(0,2,10) 0 X 2 X 4 X 6 X 8 X 10 X 12 X 14 X 16 X 18 X |

|----------------------------------------------------------|

|----------------------------------------------------------|

#### Dec(start, increment, count)

This function generates a total of **count** labels that begin at **start** and decrease by **increment** each time. It is equivalent to calling *Inc(start, -increment, count)*.

#### IncString("string", start, increment, count)

This function behaves identically to the **Inc** function, except that the incremented label values are appended to the **string**.

| IncString("VAL",1,1,8) | VAL1)VAL2)(VAL3)(VAL4)(VAL5)(VA | ALG ( VAL7 ) VAL8 ( |

|------------------------|---------------------------------|---------------------|

|------------------------|---------------------------------|---------------------|

#### Range(start, finish, count)

This function generates **count** state labels, evenly distributed over the range of values from **start** to **finish** inclusive.

Range(2,0,9) 2 X1.75X 1.5 X1.25 X 1 χ0.75 χ0.5 χ0.25) 0

#### RandomIntegerArray(count, Range\_to\_zero) or RandInt(count, Range\_to\_zero)

This function generates random state values for waveforms. **Count** indicates the number of integers to generate. The integers are random values within an inclusive range of 0 to

#### Range\_to\_zero.

#### Rep((list), count)

This function repeats **list count** number of times. The **list** can either be a literal list (e.g., (1,3,4) or ("red", "green", "blue")) or it can be a function that generates a list (e.g., **Inc**, **Dec**, or **Rep**). If the list contains words, place them in quotes. Note that the list must be placed in its own pair of parentheses.

| Rep((Dec(4,1,3),"One"),2) 4 (3) 2 (One) 4 3 2 (One) |

|-----------------------------------------------------|

|-----------------------------------------------------|

#### Hex(list)

This function formats the items in **list** as hexadecimal. All numbers in the list are converted to a base-16 representation. The letters a-f are lowercase, and the numbers are prefixed by **'h** to indicate that they are hexadecimal. By default, all numbers in the list are formatted to the same number of digits, adding leading zeros as necessary. If a MSB and LSB for the signal are specified in the *Signal Properties* dialog, all numbers will be formatted to display the given number of bits.

| Hex(RandInt(6,255))[7:0] hc7(h1 (haf) hfb (h4a) h92 ( |

|-------------------------------------------------------|

|-------------------------------------------------------|

#### Bin(list)

This function formats the items in **list** as binary. All numbers in the list are converted to a base-2 representation. The numbers are prefixed by **'b** to indicate that they are binary. By default, all numbers in the list are formatted to the same number of digits, adding leading zeros as necessary. If a MSB and LSB for the signal are specified in the *Signal Properties* dialog, all numbers will be formatted to display the given number of bits.

| Bin(Inc(0,5,6))[3:0] | <u>"60000,"60101,"51010,"51111,"60100,"51001</u> , | _ |

|----------------------|----------------------------------------------------|---|

|----------------------|----------------------------------------------------|---|

#### Skip(count)

This function causes a number of segments to be skipped (left unchanged) by the equation.

#### File("filename.txt")

This function imports a set of state values from the specified text file. This is an easy way to import values generated in a program such as MatLab, Mathematica, or a user-written C program. In the file, each state value should be on a separate line.

#### Signal("signalname")

This function copies the states from the signal indicated by *signalname* and applies them to the current signal. If no *signalname* is specified then the function returns the array of states of the current signal (this is useful when working with the **map** function).

#### map{operations} list

The **map** function allows you to perform a set of operations on every state in a state array. The first argument to the **map** function is the set of operations to perform, enclosed in curly brackets **{ }**. The second argument is the list whose elements are to be operated on. The special variable **\$\_** is used to represent the state value to be operated on (it takes on the value of each state in the list). Once you become familiar with it, the **map** function in combination with standard Perl language operations gives you extraordinary expressive power. See <u>Chapter 15</u>[191] for more information on Perl. For example the **map{\$\_+ 5} Signal()**. The **Signal** function returns a list of the states on the current signal, and the **map** function increments each state in the array by 5.

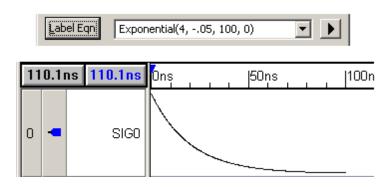

#### Analog state label functions

Analog state label equations are covered in <u>Section 8.3 Sine</u>, <u>Capacitor</u>, <u>Ramp</u>, and <u>Exponential</u> <u>waveforms</u> [120] and covers **Sin**, **SinStart**, **SinEnd**, **CapCharge**, **CapDischarge**, **Ramp**, and **Exponential**. This is an older method of generating analog waveform data and these equations generate "one-time" results (the generated events react thereafter the same as if you had manually drawn these events). Unlike the Waveform Equation Blocks described in <u>Section 8.2</u>: <u>Waveform</u> <u>Equation Blocks for editable Analog waveforms</u> [16], the original equation cannot be changed to change the waveform, only the individual events can be edited.

#### User-defined state label functions

Users can also add new functions by placing them into the perl script **labelequation.pm** located in the **SynaptiCAD > Perl** directory. Normally, state label equations are entered using the *Signals Properties* dialog, but they can also be placed in a perl script. Perl scripts are useful for creating especially complex waveforms. The file **wfm\_analog\_example.pl** in the perl directory has an example of using a label equation inside of a Perl script.

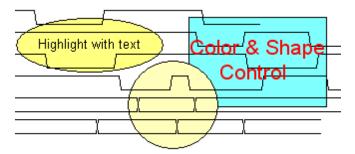

# 1.4 Colors, Line Type, Size, and More Visual Controls

There are many ways to control how signals and waveforms are displayed including color, font, line thickness, edge slant, and signal spacing.

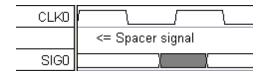

#### Insert Spacer Signals:

• Press the **Add Spacer** button to insert a horizontal space into the diagram below the selected signal.

#### Grid Lines on Signals:

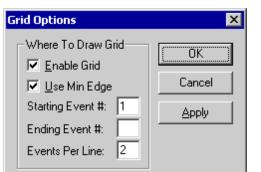

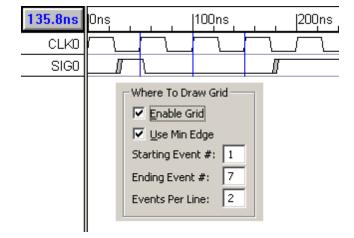

Double click on a signal name to open the Signal Properties dialog, then press the Grid Lines button to open the Grid Options dialog (see Section 2.3 Grid Lines on Clocks and Signals 44)).

|      | Ons | <br> 50r | ns       |   | 100 |

|------|-----|----------|----------|---|-----|

| SIGO |     |          | <u> </u> | 1 |     |

| SIG1 |     |          |          |   |     |

| SIG2 |     |          | 1        |   |     |

• The grid lines will still be visible if the controlling signal is hidden and the **View > Show Hidden Text** menu is checked. This lets you create patterns of grid lines without having the attached signal disturbing the circuit information.

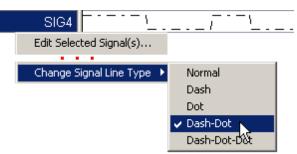

#### Individual Waveform Settings with right click menus and Signal Properties dialog:

• Line type: right click on the signal name and choose Change Signal Line type to pick a different line type like Dashes or Dots. (Line thickness is a global controls shown below)

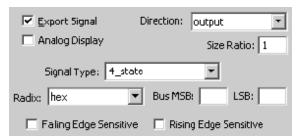

- Height of one Signal: double click on the signal name to open the Signal Properties dialog and set the Size Ratio to increase the height of the signal.

- Height of all Signals: Select the Options > Drawing

Preferences menu to open the Drawing Preferences dialog. The Waveform Height sets the height of all of the waveforms.

- Arrows on waveform edges: double click on the signal name to open the Signal Properties dialog and check the Falling Edge Sensitivity or Rising Edge Sensitivity boxes. These are also used by TestBencher Pro for sequence recognition.

| Signal Properties ?                                                   | X |

|-----------------------------------------------------------------------|---|

| Name: SIG5 Active Lo                                                  | w |

|                                                                       | _ |

| Signal Properties                                                     |   |

| ✓ Falling Edge Sensitive     ✓ Rising Edge Sensitive       SIG1     ✓ |   |

#### Global Signal Waveform Controls using the Drawing Preferences Dialog:

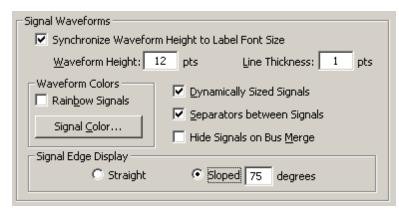

- Select the Options > Drawing Preferences menu to open the Drawing Preferences dialog and look at the Signal Waveforms section.

- Synchronize Waveform Height to Label Font Size keeps the waveform height relative to the height of signal label font.

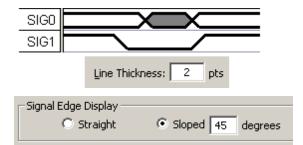

- Line Thickness can be increased and the edges can be made Straight or Slanted. In the picture, the signals have a thickness of 2 and a slant of 45% (default is 75%).

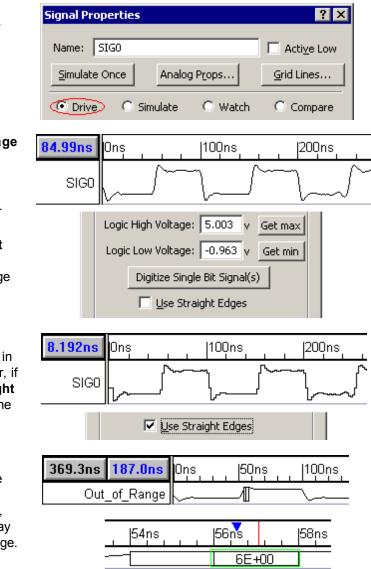

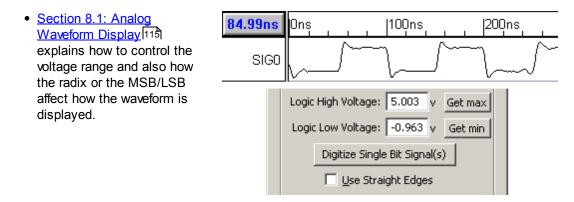

- To make straight edges for just one signal, clock, or an Analog Signal, check the **use straight edges** in the *Analog Properties* dialog, see <u>Section 8.1 Analog Waveform</u> <u>Display</u> 115.

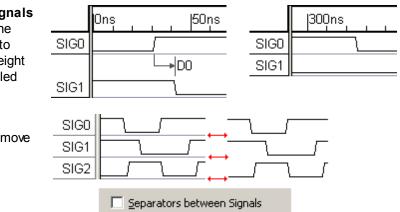

- Dynamically Sized Signals , if checked, will allow the space between signals to automatically change height as parameters are scrolled off the screen.

- Uncheck Separators Between Signals to remove the grey lines between signals.

• Hide Signals on Bus Merge hides the member signals when a group bus is created, see <u>Section 3.2: Group Bus</u> 53.

#### Global Controls that effect text inside signal waveforms using the Drawing Preferences Dialog:

Select the Options > Drawing Preferences menu to open the Drawing Preferences dialog and look at the Text Inside Signal Waveforms section.

| 1 |                             |           |   |                                         |

|---|-----------------------------|-----------|---|-----------------------------------------|

|   | Default Radi                | ⊻ hex     | - | White                                   |

|   | ⊻irtual State Text Alignmen | it: Right | • | Valid Segment Background: 🔿 Transparent |

| [ | -Text Inside Signal Wavefor |           |   |                                         |

• Virtual State Text Alignment controls whether the virtual state text in a segment will appear centered, left-justified, or right-justified.

| SIGO ( ) Blue )                    |

|------------------------------------|

| Virtual State Text Alignment: Left |

| SIGO (Blue )                       |

- **Default Radix** specifies the base in which signal values are displayed for all new signals. Individual control is in the *Signal Properties* dialog.

- In DataSheet Pro, the Valid Segment Background setting specifies whether the background color of a valid segment will over write other objects like markers and text objects.

|   | ansparent )(          | ( white b                   | ackground ) |

|---|-----------------------|-----------------------------|-------------|

|   |                       |                             |             |

| Ň | Valid Segment Backgro | ound: • Transpar<br>C White | rent        |

#### **Color Controls for Waveforms and Signal Names**

• Color One Waveform: right click on signal name and choose Change Signal Color . A global setting for all signals is shown below

- Color All Waveforms: SIG2 Choose Options > Drawing SIG3 Preferences to open the dialog. SIG4 Drawing Preferences (Style Sheet) SIG5 . . . • Rainbow Signals changes the signals to SIG6 Waveform Colors multi-colored waveforms. Rainbow Signals SIG7 • Signal Color changes Signal <u>C</u>olor... SIG8 the color of all of the signals in the diagram SIG9 (this only works if SIG10 rainbow signals is SIG11 unchecked).

- Color of Label Window and Drawing Window: Choose the Options > Text/Color Preferences menu. There are several sub-menus that are used to set the different font and color properties. The Active menus change the current diagram. The New menus change the default settings for new diagrams.

| Options Window Help Display Unit [ns] |                                                                     |                                     |

|---------------------------------------|---------------------------------------------------------------------|-------------------------------------|

| <u>T</u> ext/Color Preferences        | Active Diagram Font Preferences ><br>New Diagram Font Preferences > |                                     |

|                                       | Diagram Window <u>C</u> olor 🔹 🕨                                    | Diagram Button Bar Color            |

|                                       | Rich Text Support                                                   | Drawing Window Background Color     |

| -                                     |                                                                     | Signal Label Background Color       |

|                                       |                                                                     | Parameter Window Background Color 🗟 |

|                                       |                                                                     | Parameter Header Color              |

|                                       |                                                                     | Report Window Background Color      |

Simulated signals by default are displayed using purple signal color, but they can be made to display using the normal signal color by unchecking the View > Show Default Simulated Signals color menu.

#### Global Signal Name Controls using the Drawing Preferences Dialog:

Select the Options > Drawing Preferences menu to open the Drawing Preferences dialog and look at the Signal Names section.

| Signal Names              |

|---------------------------|

| Signal Label <u>F</u> ont |

| Font: Arial, 10 pts       |

| 🔽 Right Justify           |

| 🔲 Autosplit Long Names    |

| Autosplit Cha <u>r</u> ;  |

| 🔽 Show Direction Icons    |

| Show Index Numbers        |

|                           |

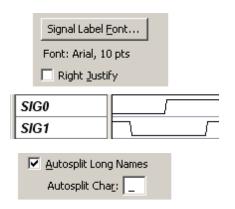

- Signal Label Font changes the font used for signal names.

- **Right Justify** causes the signals names to be lined up on the right side of the label window. Un-checking it causes it to be left justified.

- Autosplit Long Names: allows the program to split signal names that are too long for the display. They will be split at the Autosplit Char.

• Hide the index and direction columns in the signal label window by unchecking the Show Direction Icons and Show Index boxes.

| Drawing Preferences (Style Sheet) |     |  |

|-----------------------------------|-----|--|

|                                   |     |  |

| Show Direction Icons              |     |  |

| Show Index Numbers                |     |  |

| 0 < clk ↔                         | clk |  |

#### Width of the Label window:

• Drag-and-drop the bar separating signal names and signal waveforms.

| -124.9ns | UNS      |

|----------|----------|

| CLKO     |          |

| SIGO     | <b>*</b> |

|          | CLKO     |

#### Change the default naming conventions of the Label window:

- Right-click on the Add Signal button to open the Modify Auto Name Prefix dialog.

- Enter the new prefix so that each new signal will be named Prefix#, instead of the default Sig#

### 1.5 Measuring Time and State values

There are several different ways to measure and display times and state values.

#### Time and Delta Buttons

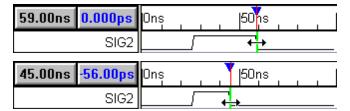

- The **Time Button**, with the black writing, displays the current position of the mouse cursor in the *Diagram* window. The **Delta Button**, with the blue writing, displays the difference between the mouse cursor and the delta mark (an upside-down, blue triangle) on the timeline above the *Diagram* window.

- To measure, left click on an edge (to select it and also move the delta mark), then move the mouse over another edge. The Delta button will

| 56.00ns 26.00ns | Ons | <b>50</b> ns |

|-----------------|-----|--------------|

| SIGO            |     | {            |

display the difference between the mouse position and the blue mark.

- To turn off the continuous measurement in the buttons, choose the **Options > General Preferences** menu to open a dialog and then uncheck the **Continuous Measurement** box.

- **Continuous Measurement:** If checked, then the black and blue digital readouts continuously update as the mouse cursor moves. Uncheck this box if the flicker bothers you. Default is checked.

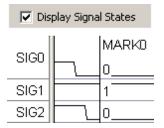

#### Display Signal States by clicking in the time line

• Click in the timeline in the *Diagram* window to drop a temporary marker line that displays the numerical state of each signal.

| 0.000ps | Ons | 1 <b>7.92 ns</b> 50ns |

|---------|-----|-----------------------|

| SIGO    |     | ĩ                     |

| SIG1    |     | 1                     |

| SIG2    |     | 0                     |

#### Display Signal States by hovering over a state transition or bus segment

• The mouse tool-tip displays the next and previous states of bus segments when the bus hovers over a state transition. This feature can be disabled by unchecking the **View > Show State at Cursor** menu.

| :  350ns | 400ns                                                              | 450n                    |

|----------|--------------------------------------------------------------------|-------------------------|

|          | Å.<br>₱17541 23808 4A4<br>Prev State: 18EFFA<br>Next State: 117541 | ю) <mark>933878)</mark> |

• Bus states automatically show partial extended state data when the segment is too small to show entire state in diagram window.

Copyright © 2011, SynaptiCAD Sales, Inc.

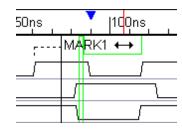

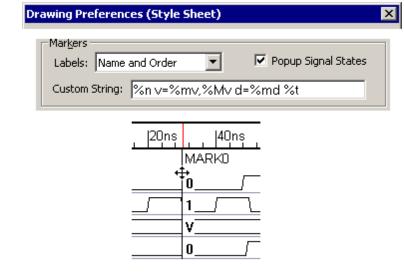

#### **Display Signal States using Markers**

- Select the **Marker** button and right click in the timing diagram to add a Marker. Hovering over a marker will show the state values of the signals at that time. To disable this feature, uncheck the **Popup Display Signal States for Markers** checkbox option in the *Drawing Preferences* dialog.

- To permanently display the state values beside a marker, double click on the marker and check the **Display Signal States** checkbox in the *Marker Properties* dialog.

| Add Bus<br>Add Spacer | Delay Setu<br>Hold Tex |         |

|-----------------------|------------------------|---------|

| -31.59ns              | s  10n:                | s  20   |

|                       | MARKO                  |         |

| Sample[]              |                        |         |

| SIGO                  | <u>∖₀_</u>             | <u></u> |

| SIG1                  | Д1¬                    |         |

| V Dis                 | olay Signal Sta        | ates    |

#### Using the Edge Properties Dialog to Measure Times and States

- Double click on the edge to open the *Edge Properties* dialog which displays the min and max times and uncertainty. Entering a new time moves the edge.

- The **min uncertainty** edit box lets you add a minimum uncertainty region to an edge. If no delays cause an uncertainty greater than the transition's minimum uncertainty, the transition will be given its minimum uncertainty value.

- The **Uncertainty =** Xns displays the actual width of the uncertainty region.

| dge Properties     |

|--------------------|

| Edge Placement     |

| Min: 30            |

| Max: 30            |

| Min Uncertainty: 0 |

| Uncertainty =0 ns  |

| 🔲 Locked           |

- If checked, the Locked checkbox fixes a transition at a specific time. This also indirectly locks any transitions connected to the locked transition by a defined timing path. Clock transitions are always locked.

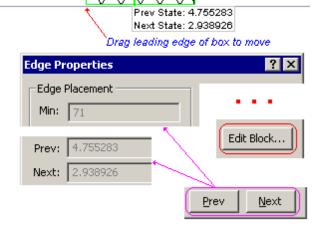

- The **Prev** and **Next** boxes display the states on the buses. This is particularly useful when the states are very close together.

| 73.1ns | 143.1ns  | Ons | 50ns |

|--------|----------|-----|------|

| В      | US0[7:0] | 0A  | OB   |

|        | Prev:    | )A  | -    |

|        | Next: 0  | )B  |      |

E

• The **Prev** and **Next buttons** moves the dialog to the previous or next edge on the signal.

# Prev <u>N</u>ext

#### Generate a Timing Analysis Report

To figure out how the time for a particular edge is calculated, you can generate a Timing Analysis Report.

- Choose File > Save Timing Diagram As and select Timing Analysis Report from the Save As Type box.

- When the file is saved, it will also be opened in a tab in the Report window. If you cannot see the Report window, choose the Window > Report.

| Report - multdely.txt                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syncad Product Version: 11.18<br><begin_timing_analysis_report><br/>[Delay Formula]<br/>A1.min (40 ns) = 40.0<br/>A1.max (80 ns) = 80.0<br/>A1.min (40 ns) = 40.0<br/>A1.min (40 ns) = 40.0<br/>B1.min (10 ns) = 10.0<br/>B1.max (50 ns) = 50.0<br/>B1.min (10 ns) = 10.0<br/>B1.max (50 ns) = 50.0</begin_timing_analysis_report>                                                                                                                   |

| [Interim Parameter Equation]<br>SIG1.0.A1.min (50 ns) = A1.min (40 ns) + SIG0.0<br>SIG1.0.A1.max (90 ns) = A1.max (80 ns) + SIG0.0<br>SIG2.0.A1.min (50 ns) = A1.min (40 ns) + SIG0.0<br>SIG2.0.A1.max (90 ns) = A1.max (80 ns) + SIG0.0<br>SIG3.0.B1.min (30 ns) = B1.min (10 ns) + SIG0.1<br>SIG3.0.B1.max (70 ns) = B1.max (50 ns) + SIG0.1<br>SIG1.0.B1.min (30 ns) = B1.min (10 ns) + SIG0.1<br>SIG1.0.B1.min (70 ns) = B1.max (50 ns) + SIG0.1 |

| [Resolved Edge Equation]<br>SIG1.0.min (30 ns) = min(SIG1.0.A1.min (50 ns),<br>SIG1.0.max (70 ns) = min(SIG1.0.A1.max (90 ns),                                                                                                                                                                                                                                                                                                                       |

| <pre><end_timing_analysis_report></end_timing_analysis_report></pre>                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Errors / Differences / Grep / TE_parse.log / TE Results / multdely.txt)                                                                                                                                                                                                                                                                                                                                                                              |

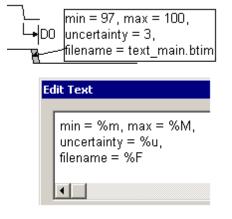

Display time using Text objects, Parameters, or Markers

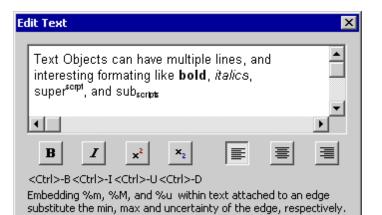

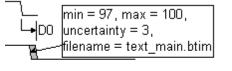

• Use a Text Object with control codes to display edge times: press the Text button, select the edge, then right-click to open an edit box. Enter %m, %M , or %u control codes to display min transition, max transition, or uncertainty region ( Section 6.1: Adding Text 91).

• Display the distance between two transitions: Add a setup or hold parameter between the two transitions. Double-click on the parameter to open the *Parameter Properties* dialog, and choose the **Distance** from the Display label drop-down, and optionally check the **Outward arrows** box (Section 5.3 Display Settings for <u>Parameters</u> [80]).

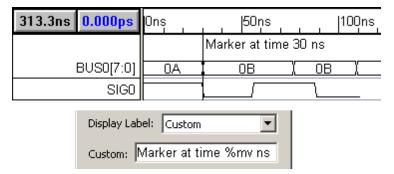

• **Display the exact placement of a time marker**: Press the **Marker** button the right-click in the diagram to add a time marker line. Double-click on the marker line to open the *Edit Time*

*Marker* dialog and change the Display label to **min value** or **custom** using the **%mv** control code (Section 6.4 Markers Lines 96).

# **1.6 Shifting, Clearing, and Moving Edges**

The *Edit Waveform Edges* dialog operates on the edges of the selected signals. The edges can be removed, shifted in time, or transformed using a equation.

#### To Edit Waveform Edges:

- Select the signals you wish to modify in the diagram window. Note: If no signals are selected, all signals will be modified except clocks and group buses.

- Select the Edit > Edit Waveform Edges menu to open the Edit Waveform Edges dialog.

- The **Range** section defines the time range over which to operate.

- Clear Edges in Range deletes all the edges but leave a blank waveform.

- Delete Edges in Range and Shift back edges after range to deletes all the waveforms and remove that section of time.

- Shift Edges in Range to quickly shift the edges by a positive or negative amount of time.

| Edit Waveform Edges                                   | ×  |

|-------------------------------------------------------|----|

| Range:<br>From: -0.001 ns To: 159                     | ns |

| Edit:                                                 |    |

| ⊂ ⊆lear Edges in Range                                |    |

| C Delete Edges in Range, Shift back edges after range |    |

| C Shift Edges in Range:                               |    |

| Amount of time to shift: 100                          | -  |

| • Iransform Edge Times in Range:                      |    |

| Edge Time Equation: \$time + 100                      | •  |

| OK Apply Close                                        |    |

Choose Transform Edge Times in Range, to apply an equation to all the edges. The variable that represents the current time for the edge is \$time.

An example of an edge equation is:

```

($time + 10)/(4)

```

This will take the current time, add ten, and then divide the result by four. Note that this function can also be used to shift edges in a range, but the dedicated shift function is considerably faster.

• Click the **Apply** or **OK** button to modify the waveform edges. Applying will leave the *Edit Waveform Edges* dialog open for other waveform modifications.

### 1.7 Copy Signals or Waveforms

Signals or sections of waveforms can be copied and pasted. The block copying of waveforms can be used to copy whole transactions, like a read cycle, and paste it as needed throughout the diagram.

#### Copy a signal:

- Select one or more signal names, and then choose the Edit > Copy Text and Signals menu. Now the signals and any objects attached to the signals, like text objects and parameters, are copied to the clipboard.

- Paste the signals using the Edit > Paste menu option, into either the same timing diagram or into another timing diagram.

#### Copy a portion of the waveforms (a time slice):

- Select the names of the signals that you want to copy. If no signals are selected, then the copy will operate on all of the signals in the diagram (this is the most common usage).

- Choose the Edit > Block Copy Waveforms menu option to open the Block Copy Waveforms dialog.

| Block Copy           | Waveforms                                | ? × |

|----------------------|------------------------------------------|-----|

| Choose th            | ne Start, End, Place At units            |     |

| C Time               | Clock Cycles     Controlling Clock: CLK0 | •   |

| Start:               | 0 cycles, Ons 💿 Insert                   | 1   |

| End:                 | 5 cycles, 500ns Overwrite                |     |

| Place At:            | 5 cycles, 500ns # of ⊆opies: 1           |     |

| Change W             | Vaveform Destination                     |     |

| SIGO                 | SIGO                                     |     |

| SIG0<br>SIG1<br>CLK0 | SIG0<br>SIG1                             |     |

|                      |                                          |     |

|                      | OK Cancel Help                           |     |

- Choose either Time or Clock Cycles for the base units of the dialog.

- If you are copying just signals (no clocks) then time is the default base unit of the dialog.

- If you are copying part of a clock then it is best to choose a **clock cycles** base unit and choose the copied clock as the **controlling clock**. If you select **time** when copying clocks, the (*end\_time start\_time*) must equal an integral number of clock periods, and

the *place\_at* time must be at the same clock period offset as the *start\_time*.

- The **Start** and **End** define the range of the block to be copied, and the **Place At** is the time that at which the block will be pasted.

- The **Insert** and **Overwrite** radio buttons determine whether the paste block will be inserted into the existing waveforms or overwrite those waveforms.

- The list box at the bottom of the dialog determines which signal the copied waveforms will be pasted into. To change this mapping select a row and then use the drop-down box to choose a different destination signal.

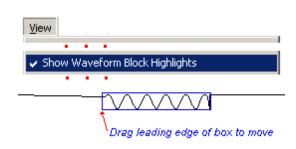

#### Short-Cut Method for Waveform Block Copy

- Select the names of the signals that you want to copy. If no signals are selected, then the copy will operate on all of the signals in the diagram (this is the most common usage).

- Hold the <CTRL> key while *clicking and dragging the mouse across the time line* to select the start and end times of the block. When you release mouse the Block Copy Waveforms dialog will open with the range entered.

#### Merge two timing diagrams together:

- Open the timing diagram that will hold all of the merged signals, using File > Open Timing Diagram menu.

- Then select the **File > Merge Timing Diagram** menu and choose the second timing diagram file. This will copy the entire diagram and paste it into the first diagram.

- See <u>Section 10.4 Merging Diagrams</u> [144] for more information on resolving parameter name conflicts that might occur during a merge.

### 1.8 Referencing Waveforms from Libraries

Waveforms can also be referenced from libraries in a similar manner to parameter libraries (see <u>Chapter 10: Parameter Libraries</u> [138]). When a master waveform changes, the signals in other diagrams will also change on the next opening of the diagram. This lets you build up libraries of master signals that can be referenced by several different diagrams to show different timing shots of the circuit. The reference waveforms can be contained in external files or from signals in the same file. The Waveform library feature can also be used to display bit-slices of an existing waveform.

#### Using an External Waveform Library:

- Diagram master\_ref.btim\* Add Signal 🚺 Add Bus Setup Sample HIĠH TRI Add Clock Add Spacer Hold Marker Text 464.9ns 334.3ns Ons 150ns 1100ns MasterSig

- Create a Waveform Library by saving a timing diagram that has the master waveforms in it.